ADLINK cPCI-7300 User Manual

Page 52

44

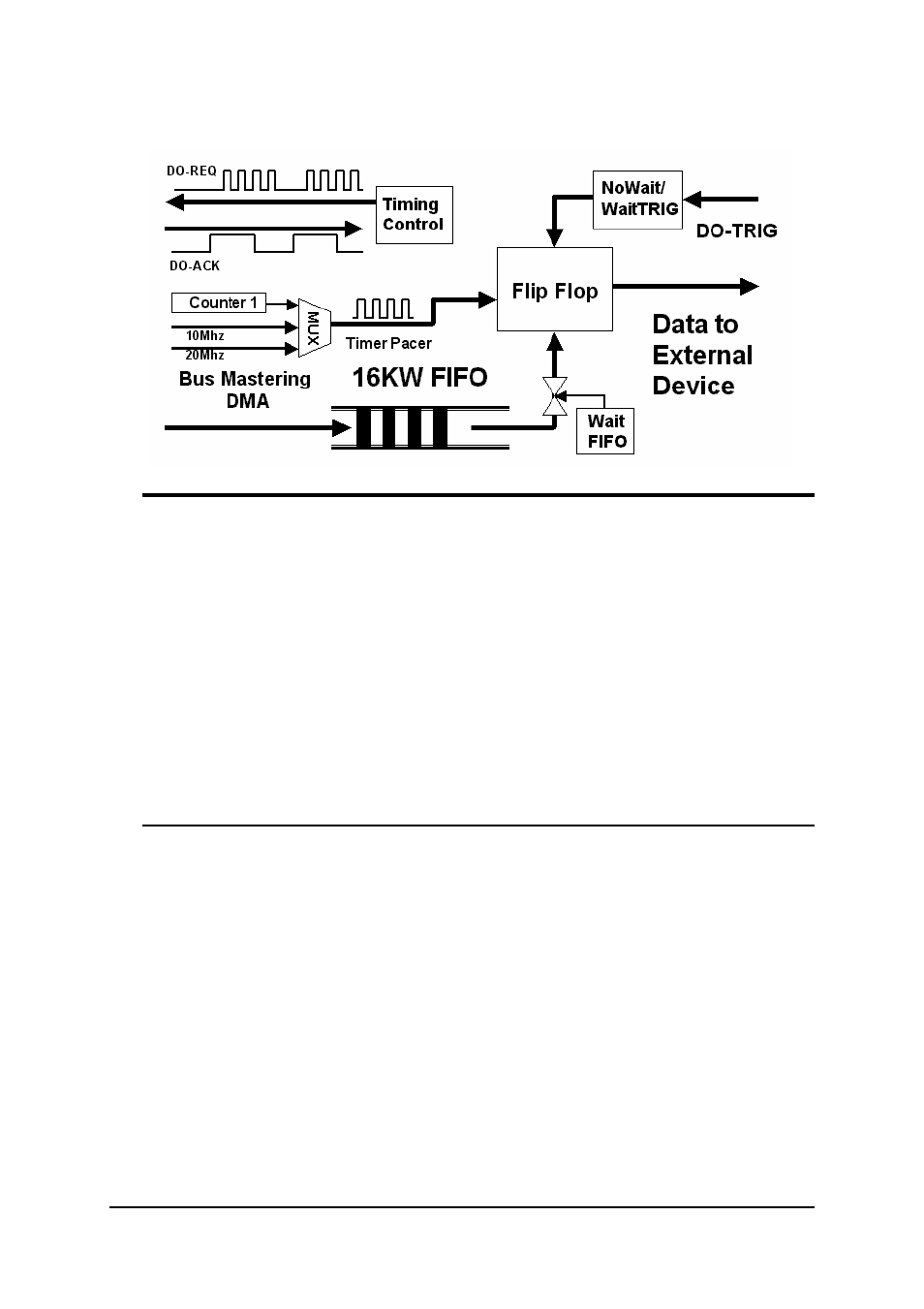

• Operation Theory

The operation flow is show as below:

Notes: When the DMA function of digital output starts, the output data will

transfer to the output FIFO of cPCI/PCI-7300A when PCI bus is

available. If the speed of translation from the FIFO on board to the

external device is higher than that from system memory to the output

FIFO or the PCI bus is busy for a long time, the FIFO become empty

and under-run situation occurs after the next data being read from the

output FIFO. Users should check the under-run status to see whether

the under-run occurs or not. Some output data will repeat when the

output FIFO is under-run.

Notes: To avoid the under-run of output FIFO when digital output starts and

PCI bus is still busy, it is highly recommended to set the starting mode

to be WaitFIFO. The higher the timer pacer rate is the larger amount

of almost empty threshold should be set to prevent the under-run

situation.

4.11.4 Pattern Generator

The digital data is output to the peripheral device periodically based on the

clock signals occur at a constant rate. The digital pattern are stored in the

cPCI/PCI-7300A’s on-board FIFO with the length of pattern less than or equal

to 16K samples.

The operations sequence of pattern generator are listed:

1. Define the input configuration to be 32-bit, 16-bit or 8-bit data width.

2. Enable or disable the active terminators.

3. Define the output timer pacer rate to be 20MHz, 10MHz, or the output

82C54 timer 1. The timer pacer controls the output rate.