7 clocking mode – ADLINK cPCI-7300 User Manual

Page 39

Operation Theory

• 31

In non-chaining mode, the maximum DMA data transfer size is 2M double

words (8M bytes). However, by using chaining mode, scatter/gather, there is

no limitation on DMA data transfer size. Users can also link the descriptor

nodes circularly to achieve a double-buffered mode DMA.

4.7 Clocking Mode

The data input to or output from the FIFO is operated in a specific rate. The

specific sampling rate or the pacer rate can be programmable by software, by

external clock, or by easy handshaking protocol.

Four clocking modes are provided in the cPCI/PCI-7300A to sample input data

to the FIFO or output date from FIFO to the external devices. They are:

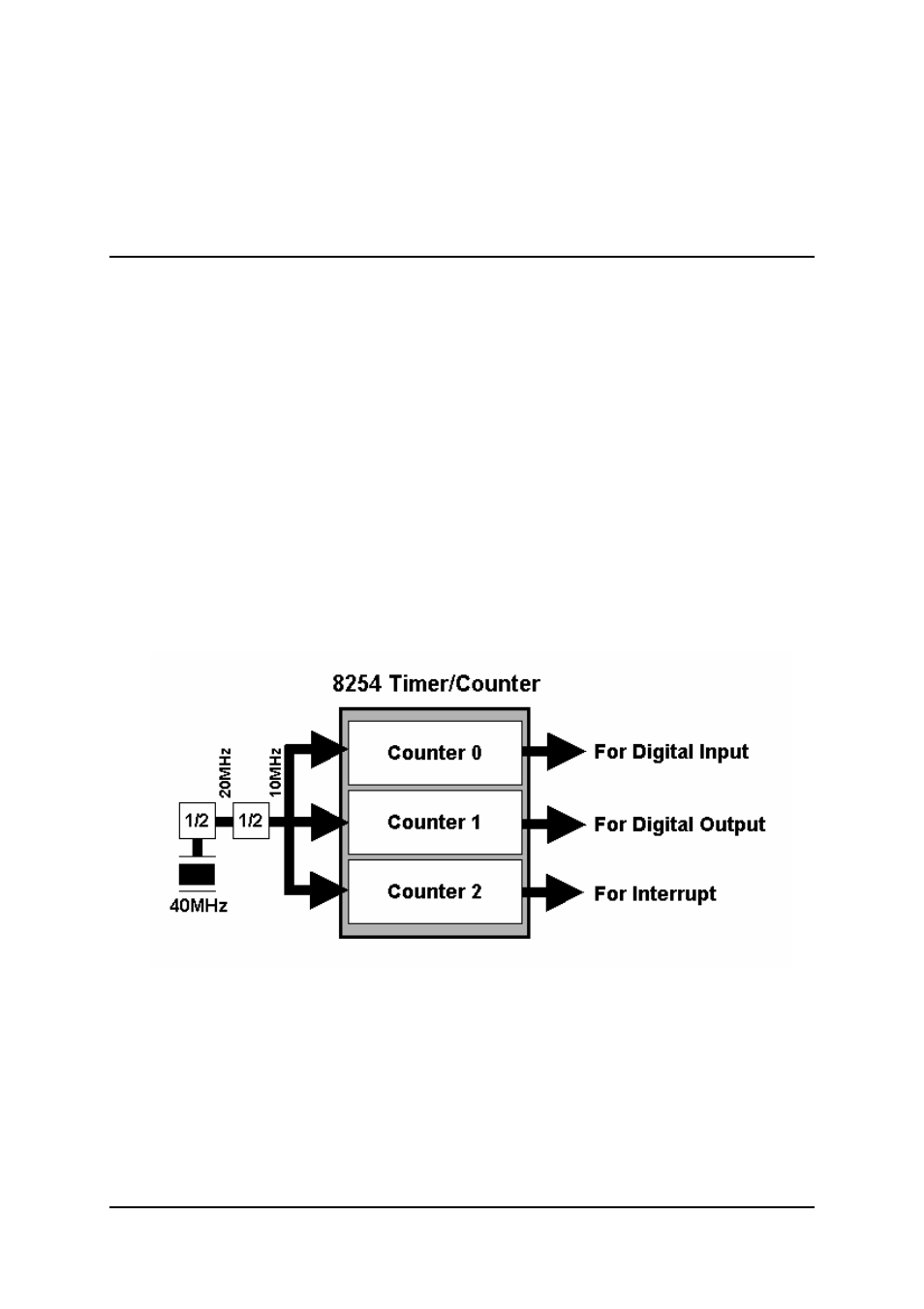

1. Internal Clock: Three sources are available to activate both digital input

and digital output. They are 20MHz, 10MHz, and programmable timer

82C54. There are three counters in 82C54, counter 0 is used to generate

sampling clock for digital input, counter 1 is used timer pacer for digital

output, and counter 2 is used for interrupt function. The configuration is

illustrated as follows.

Figure 4.8: Timer configuration

2. External Clock: This mode is only applied for digital input. The digital

inputs are handled by the external clock strobe (DI-REQ). The DI-ACK

signal reflects the almost full status of the input FIFO. The DI-ACK is

asserted when input FIFO is not almost full, which means the external

device can input data. If the input FIFO is almost full, the DI-ACK is

de-asserted, then the external device should pause data transfer and wait