6 di_fifo: di fifo direct access port – ADLINK cPCI-7300 User Manual

Page 29

Registers

• 21

T2_EN (R/W)

0: Disable Timer2 interrupt

1: Interrupt CPU on falling edge of Timer 2 output

AUXDI0_INT (R/W)

0: AUXDI does not generate interrupt

1: AUXDI interrupt occurred. Write “1” to clear

T2_INT (R/W)

0: Timer 2 does not generate interrupt

1: Timer 2 interrupt occurred. Write “1” to clear

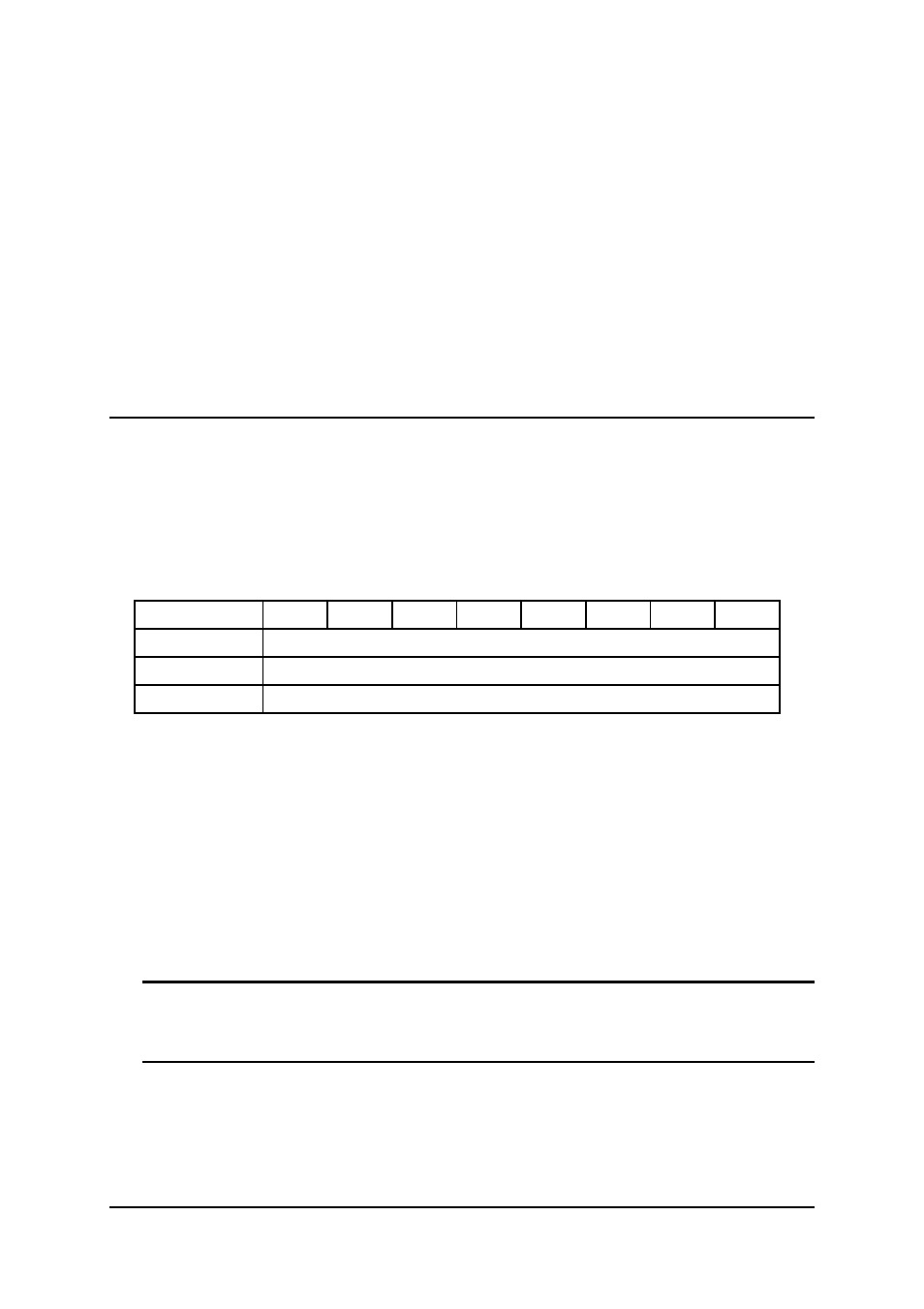

3.6 DI_FIFO: DI FIFO direct access port

The digital input FIFO data can be accessed through this port directly.

Address: BASE + 0x10

Attribute: READ/WRITE

Data Format:

Bits

7

6

5

4

3

2

1

0

Bit # 7~0

DI_FIFO_8

Bit # 15~8

DI_FIFO_16

Bit # 31_16 DI_FIFO_32

DI_FIFO_8

Bit 7 ~ Bit 0 of digital input FIFO

DI_FIFO_16

Bit 15 ~ Bit 8 of digital input FIFO if the digital input is configured as 16-bit wide

or 32-bit wide.

DI_FIFO_32

Bit 31 ~ Bit 16 of digital input FIFO if the digital input is

configured as 32-bit wide

Note: Although this port is R/W port, write operation should be avoided in

normal operation. If both PORT A and PORT B are configured as

output ports, read/write to this port is meaningless.