8 fifo_cr: fifo almost empty/full register – ADLINK cPCI-7300 User Manual

Page 31

Registers

• 23

3.8 FIFO_CR: FIFO almost empty/full register

The register is used to control the FIFO programmable almost empty/full flag.

Address: BASE + 0x018

Attribute: WRITE Only

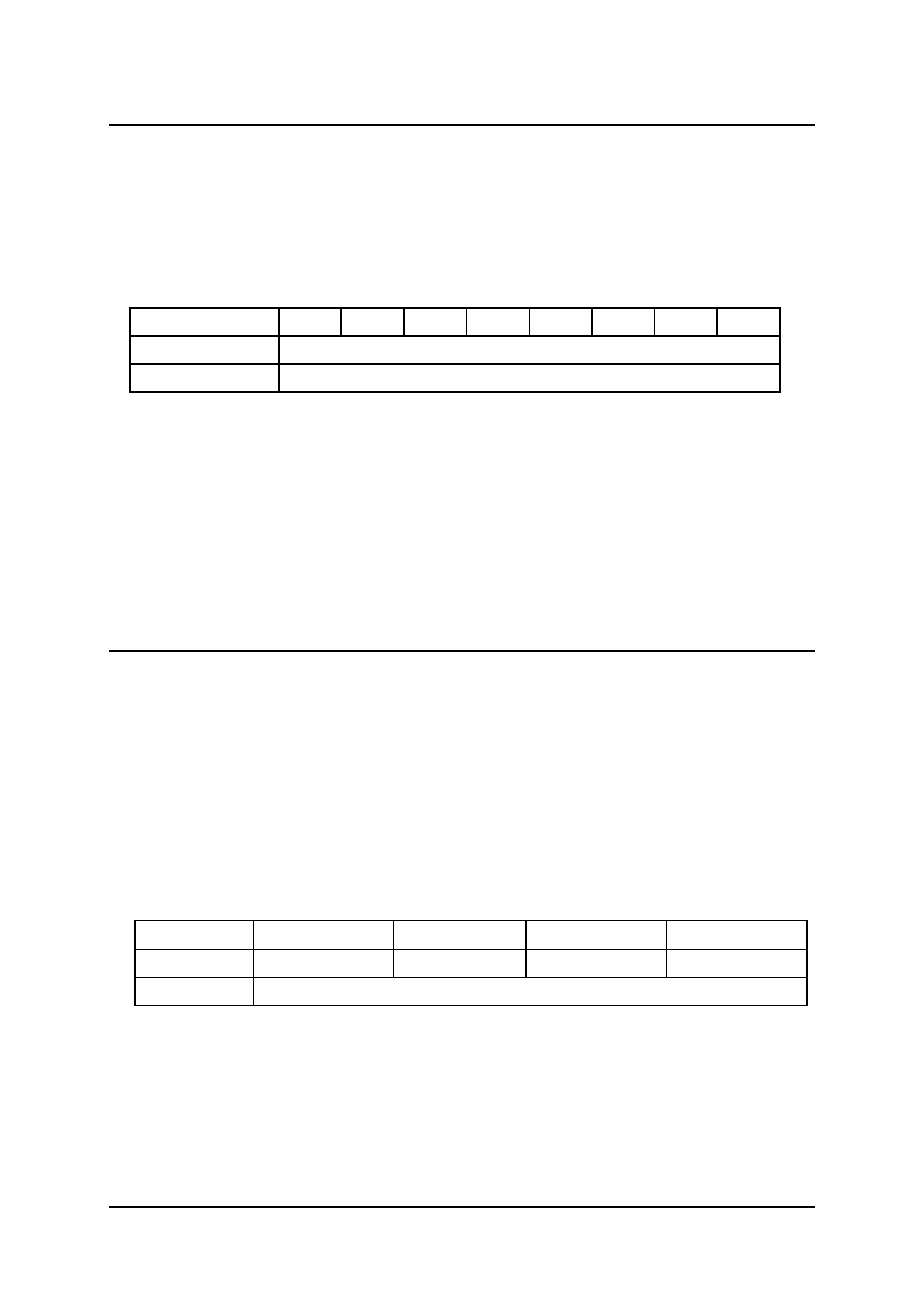

Data Format:

Bits

7

6

5

4

3

2

1

0

Bit 15~0

PB_PAE_PAF

Bit 31_16

PA_PAE_PAF

PB_PAE_PAF (WO)

Programmable almost empty/full threshold of PORTB FIFO, 2

consecutive writes are required to program PORTB FIFO.

Programmable almost empty threshold first.

PA_PAE_PAF(WO)

Programmable almost empty/full threshold of PORTA FIFO, 2

consecutive writes are required to program PORTA FIFO.

Programmable almost empty threshold first.

3.9 POL_CNTRL: Control Signal Polarity Control

Register

The register is used to control the control signals’ polarity. The control signals

include DI_REQ, DI_ACK, DI_TRG, DO_REQ, DO_ACK and DO_TRG.

Please note that this register is for PCI-7300A Rev.B and cPCI-7300 only.

Address: BASE + 0x1C

Attribute: READ/WRITE

Data Format:

Bit # 3~0

DO_REG_NEG DI_TRG_NEG DI_ACK_NEG DI_REQ_NEG

Bit # 71~4

- - DO_TRG_NEG

DO_ACK_NEG

Bit # 31~8

Don’t Cared

DI_REQ_NEQ (R/W)

0: DI_REQ is rising edge active

1: DI_REQ is falling edge active