4 auxiliary digital i/o register, 5 int_csr: interrupt control and status register – ADLINK cPCI-7300 User Manual

Page 28

20

• Registers

BURST_HNDSHK (R/W)

0: disable burst handshaking mode

1: enable burst handshake mode

* Note: This bit is for Rev.B only.

3.4 Auxiliary Digital I/O Register

Auxiliary 4-bit digital inputs and 4-bit digital outputs

Address: BASE + 08

Attribute: READ/WRITE

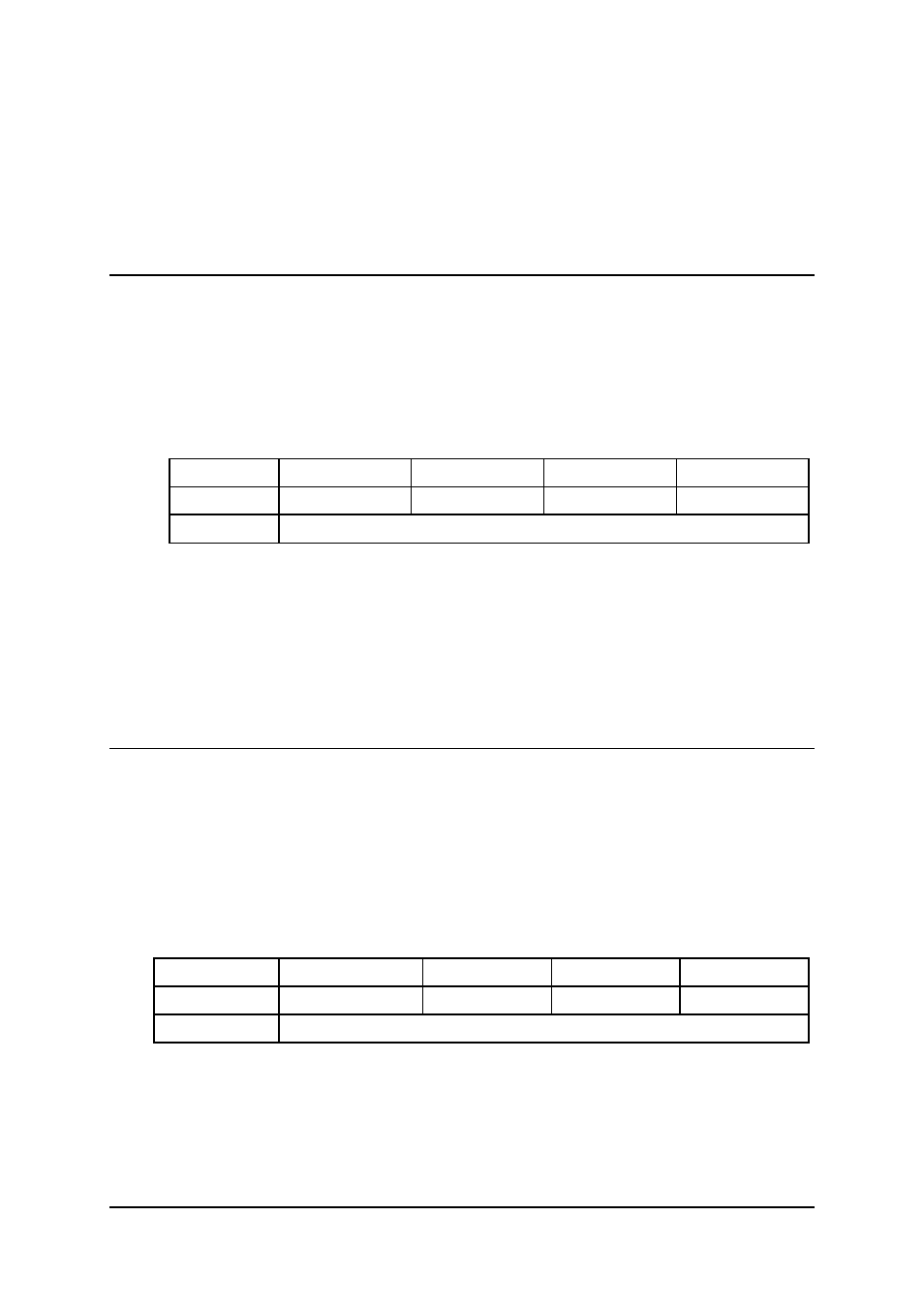

Data Format:

Bit # 3~0 DO_AUX_3 DO_AUX_2 DO_AUX_1 DO_AUX_0

Bit # 7~4 DI_AUX_3 DI_AUX_2 DI_AUX_1 DI_AUX_0

Bit # 31~8 Don’t Cared

This auxiliary digital I/O is controlled by porgram I/O only.

DO_AUX_3 ~ DO_AUX_0 (R/W)

4-bit auxiliary output port. Program I/O only.

DI_AUX_3 ~ DI_AUX_0 (R)

4-bit auxiliary input port. Program I/O only

3.5 INT_CSR: Interrupt Control and Status Register

The interrupt of PCI-7300A is controlled and status is checked through this

register.

Address: BASE + 0x0C

Attribute: READ/WRITE

Data Format:

Bit # 3~0

T2_INT AUXIO_INT T2_EN AUXDI0_EN

Bit # 7~4

- -

Reserved

Reserved

Bit # 31~8

Don’t Cared

AUXDI_EN (R/W)

0: Disable AUXDI0 interrupt

1: Interrupt CPU on falling edge of AUXDI0