3 do_csr: do control & status register, Do_csr: do control & status register – ADLINK PCI-7300A User Manual

Page 34

22

Registers

3.3 DO_CSR: DO Control & Status Register

Digital input control and status checking is done by this register.

Address: BASE + 04

Attribute: READ/WRITE

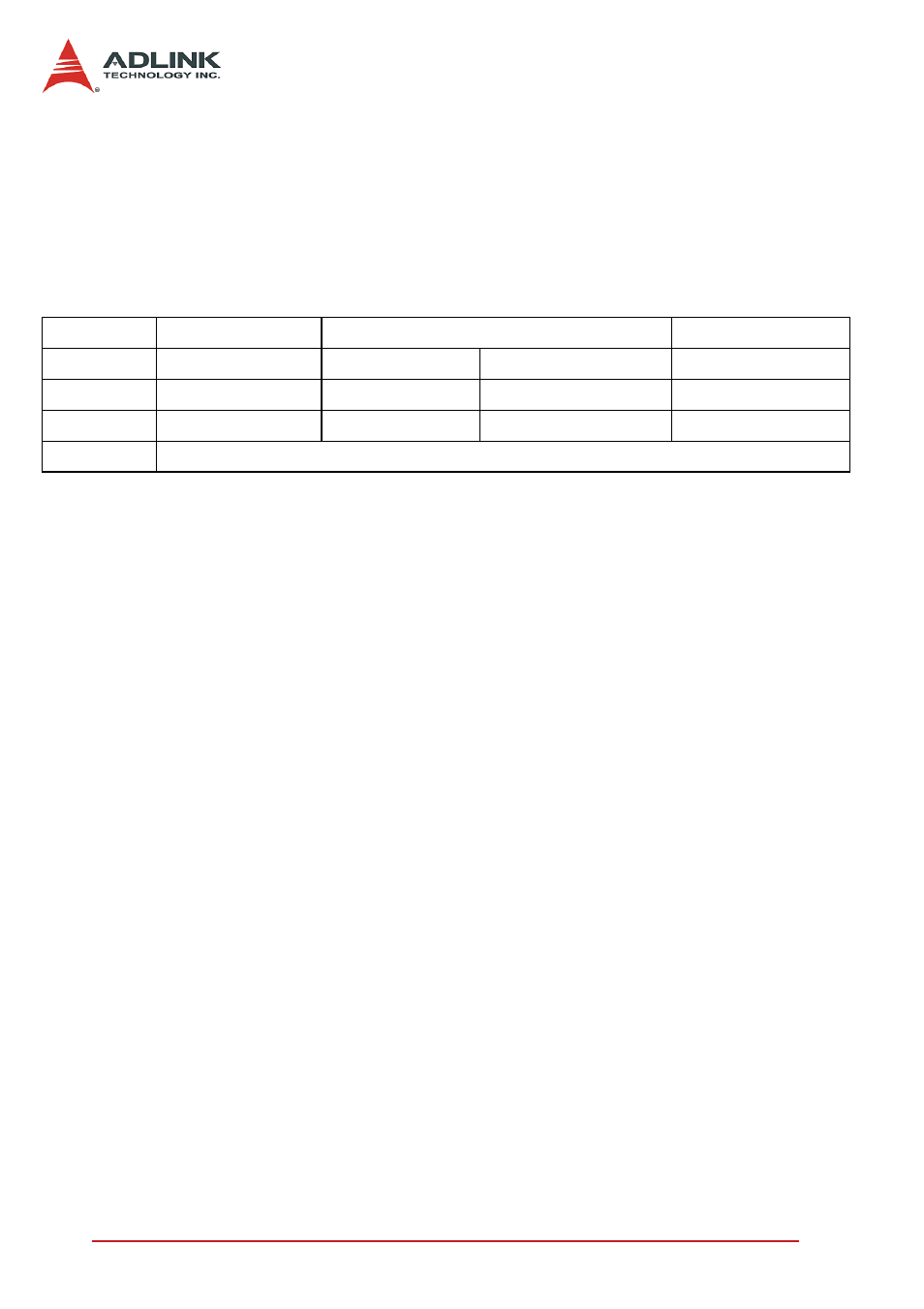

Data Format:

(2) This bit is different between Rev.A and Rev.B.

DO_32 (R/W)

X

0: Output port is not 32-bit wide ( 16-bit or 8-bit wide)

X

1: Output port is 32-bit wide, PORTA is configured as the

extension of PORTB. That means PORTB is output lines

(0…15), and PORTA is output lines (16…31). All PORTA

control signals are disabled.

DO_MODE (R/W)

X

00: use timer1 output as output clock

X

01: use 20MHz clock as output clock

X

10: use 10MHz clock as output clock

X

11: REQ/ACK handshaking mode

DO_WAIT_NAE (R/W)

X

0: do not wait output FIFO not almost empty flag

X

1: delay output data until FIFO is not almost empty

PAT_GEN(R/W)

X

0:pattern generation disable (FIFO data do not repeat dur-

ing data output)

X

1:pattern generation enable (FIFO data repeat themselves

during data output)

Bit # 3~0

DO_WAIT_NAE

DO_MODE

DO_32

Bit # 7~4

PG_STOP_TRIG PB_TERM_OFF

DO_WAIT_TRG

PAT_GEN

Bit # 11~8

DO_FIFO_FULL

DO_UNDER

DO_FIFO_CLR

DO_EN

Bit # 15~12

-

-

BURST_HNDSH (2) DO_FIFO_EMPTY

Bit # 31~16

Don’t Care