2 di_csr: di control & status register, Di_csr: di control & status register – ADLINK PCI-7300A User Manual

Page 32

20

Registers

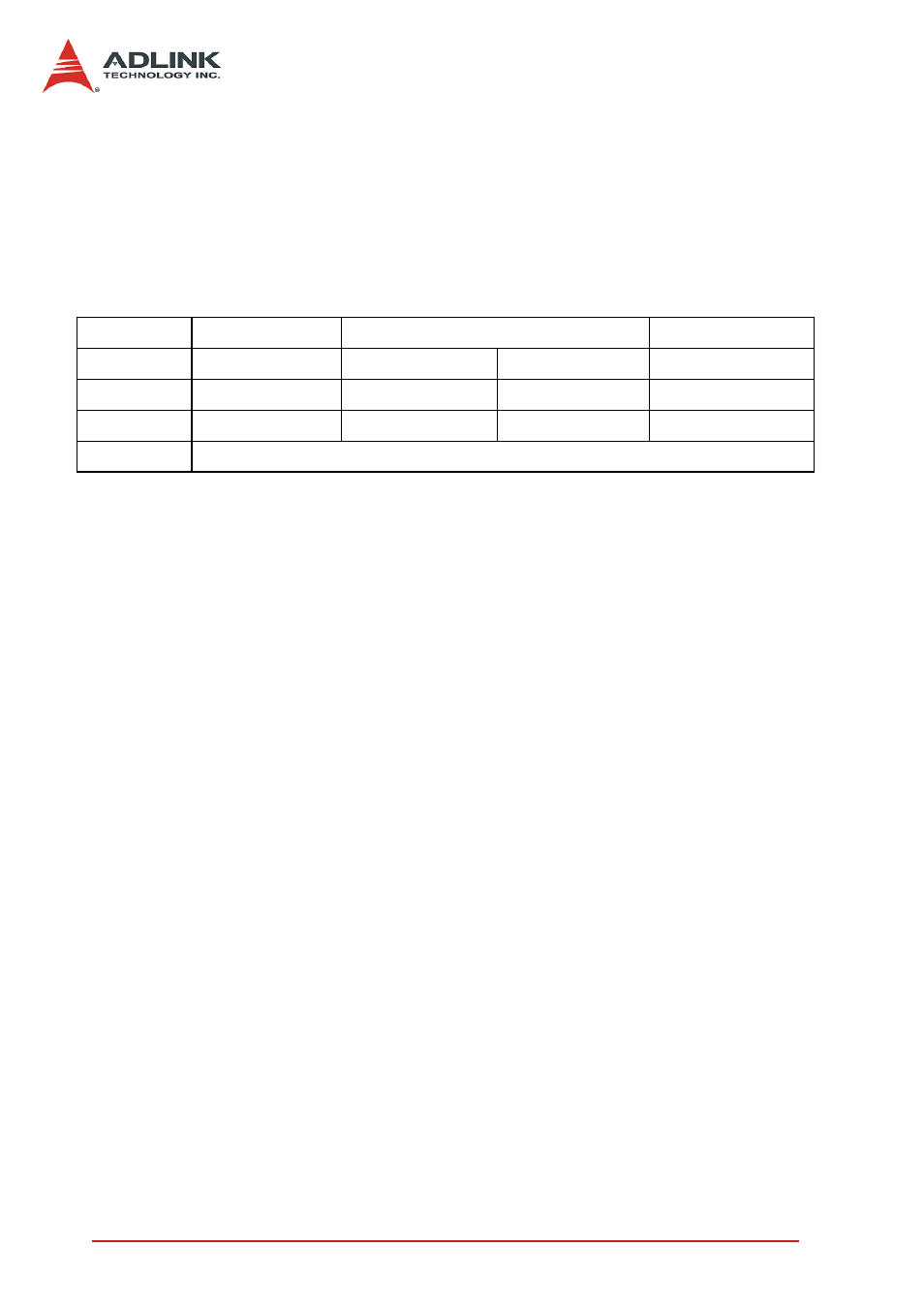

3.2 DI_CSR: DI Control & Status Register

Digital input control and status checking is done by this register.

Address: BASE + 00

Attribute: READ/WRITE

Data Format:

(1) This bit is different between Rev.A and Rev.B.

DI_32 (R/W)

X

0:Input port is not 32-bit wide (16-bit or 8-bit wide)

X

1:Input port is 32-bit wide, PORTB is configured as the

extension of PORTA. That means PORTA is input lines

0…15, and PORTB is input lines 16…31. All the PORTB

control signals are disabled.

DI_CLK_SEL (R/W)

X

00: use timer0 output as input clock

X

01: use 20MHz clock as input clock

X

10: use 10MHz clock as input clock

X

11: use external clock (DI_REQ) as input clock

DI_HND_SHK (R/W)

X

0: No handshaking

X

1: REQ/ACK handshaking mode

DI_WAIT_TRIG (R/W)

X

0: start input sampling immediately

X

1: delay input sampling until DITRIG is active

PA_TERM_OFF (R/W)

X

0: PORTA terminator ON

X

1: PORTA terminator OFF

Bit # 3~0

DI_HND_SHK

DI_CLK_SEL

DI_32

Bit # 7~4

0

PA_TERM_OFF DI_WAIT_TRIG

-- (1)

Bit # 11~8 DI_FIFO_FULL

DI_OVER

DI_FIFO_CLR

DI_EN

Bit # 15~12

-

-

-

DI-FIFO_EMPTY

Bit # 31~16

Don’t Care