5 interrupt status & control register (base + 1c), Interrupt status & control register (base + 1c) – ADLINK PCIe-7200 User Manual

Page 36

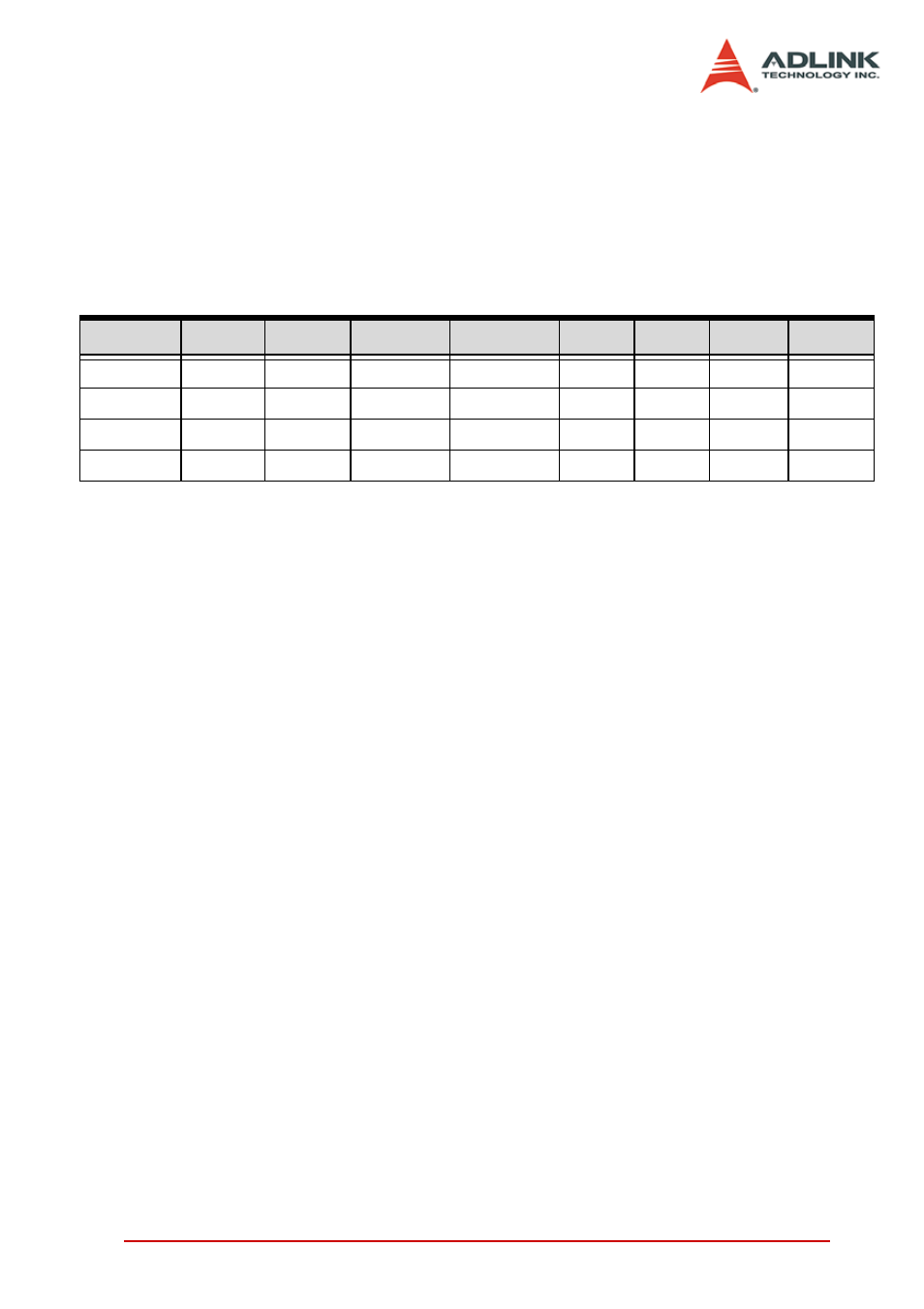

Register Format

27

3.5

Interrupt Status & Control Register (BASE + 1C)

The interrupt mode/status is set/checked through this register.

Address: BASE + 1C

Attribute: READ/WRITE

Data Format:

Interrupt Control:

With the 7200 series, interrupts can be triggered by many

signal sources such as O_ACK, I_REQ, timer 0, timer 1, and

timer 2. The following bits control the interrupt source:

IO_ACK: Interrupt is triggered by O_ACK signal.

1: O_ACK interrupt is enabled

0: O_ACK interrupt is disabled

II_REQ: Interrupt is triggered by I_REQ signal.

1: I_REQ interrupt is enabled

0: I_REQ interrupt is disabled

T0_EN: Interrupt is triggered by timer 0 output.

1: Timer 0 interrupt is enabled

0: Timer 0 interrupt is disabled

T1_EN: Interrupt is triggered by timer 1 output.

1: Timer 1 interrupt is enabled

0: Timer 1 interrupt is disabled

T2_EN: Interrupt is triggered by timer 2 output.

1: Timer 2 interrupt is enabled

0: Timer 2 interrupt is disabled

Interrupt Status:

Byte

7

6

5

4

3

2

1

0

Base +1C

SI_TO

SI_REQ SO_ACK

T2_EN

T1_EN T0_EN II_REQ IO_ACK

Base +1D FIFOFF FIFOEF FIFORST REQ_NEG T1_T2 T0_T2

SI_T2

SI_T1

Base +1E

----

----

----

----

----

----

----

----

Base +1F

----

----

----

----

----

----

----

----