Ac test loads and waveforms – Cypress Quad HOTLink II CYV15G0404RB User Manual

Page 20

CYV15G0404RB

Document #: 38-02102 Rev. *C

Page 20 of 27

Differential CML Serial Outputs: ROUTA1

±, ROUTA2±, ROUTB1±, ROUTB2±, ROUTC1±, ROUTC2±, ROUTD1±, ROUTD2±

V

OHC

Output HIGH Voltage

(V

CC

Referenced)

100

Ω differential load

V

CC

– 0.5

V

CC

– 0.2

V

150

Ω differential load

V

CC

– 0.5

V

CC

– 0.2

V

V

OLC

Output LOW Voltage

(V

CC

Referenced)

100

Ω differential load

V

CC

– 1.4

V

CC

– 0.7

V

150

Ω differential load

V

CC

– 1.4

V

CC

– 0.7

V

V

ODIF

Output Differential Voltage

|(OUT+)

− (OUT−)|

100

Ω differential load

450

900

mV

150

Ω differential load

560

1000

mV

Differential Serial Line Receiver Inputs: INA1

±, INA2±, INB1±, INB2±, INC1±, INC2±, IND1±, IND2±

V

DIFFs

[7]

Input Differential Voltage |(IN+)

− (IN−)|

100

1200

mV

V

IHE

Highest Input HIGH Voltage

V

CC

V

V

ILE

Lowest Input LOW Voltage

V

CC

– 2.0

V

I

IHE

Input HIGH Current

V

IN

= V

IHE

Max.

1350

µA

I

ILE

Input LOW Current

V

IN

= V

ILE

Min.

–700

µA

VI

COM

[9]

Common Mode input range

((V

CC

– 2.0V)+0.5)min,

(V

CC

– 0.5V) max.

+1.25

+3.1

V

Power Supply

Typ

Max

I

CC

[10,11]

Max Power Supply Current

TRGCLKx =

MAX

Commercial

910

1270

mA

Industrial

1320

mA

I

CC

[10,11]

Typical Power Supply Current

TRGCLKx =

125 MHz

Commercial

900

1270

mA

Industrial

1320

mA

CYV15G0404RB DC Electrical Characteristics

(continued)

Parameter

Description

Test Conditions

Min

Max

Unit

Notes

9. The common mode range defines the allowable range of INPUT+ and INPUT

− when INPUT+ = INPUT−. This marks the zero crossing between the true and

complement inputs as the signal switches between a logic-1 and a logic-0.

10. Maximum I

CC

is measured with V

CC

= MAX, T

A

= 25°C, with all channels and Serial Line Drivers enabled, sending a continuous alternating 01 pattern, and

outputs unloaded.

11. Typical I

CC

is measured under similar conditions except with V

CC

= 3.3V, T

A

= 25°C, with all channels enabled and one Serial Line Driver for each transmit

channel sending a continuous alternating 01 pattern. The redundant outputs on each channel are powered down and the parallel outputs are unloaded.

12. Cypress uses constant current (ATE) load configurations and forcing functions. This figure is for reference only.

13. The LVTTL switching threshold is 1.4V. All timing references are made relative to where the signal edges cross the threshold voltage.

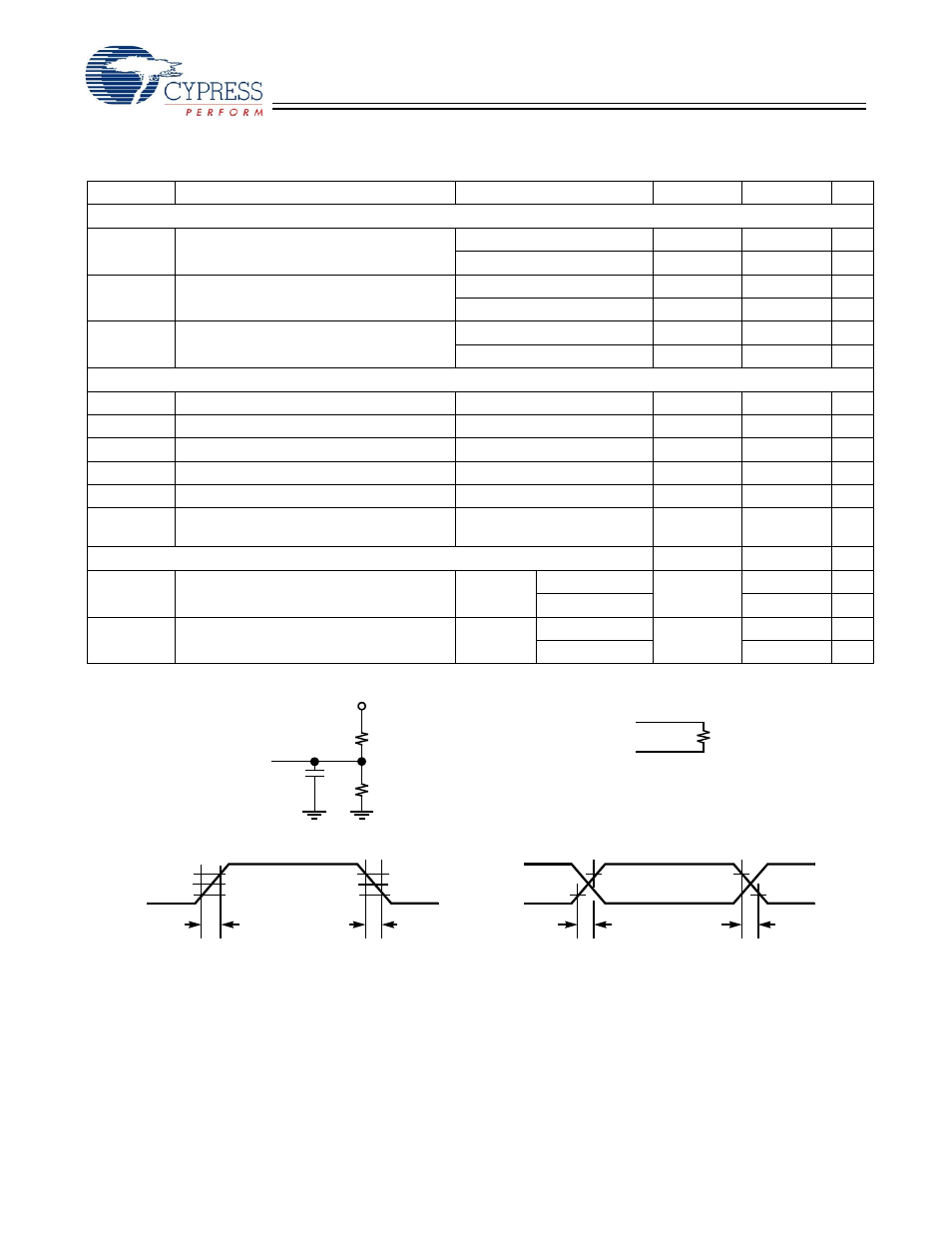

AC Test Loads and Waveforms

2.0V

0.8V

GND

2.0V

0.8V

80%

20%

80%

20%

R

L

(Includes fixture and

probe capacitance)

3.0V

V

th

= 1.4V

≤ 270 ps

≤ 270 ps

[13]

V

th

= 1.4V

3.3V

R1

R2

R1 = 590

Ω

R2 = 435

Ω

(Includes fixture and

probe capacitance)

C

L

≤ 7 pF

(a) LVTTL Output Test Load

R

L

= 100

Ω

(b) CML Output Test Load

C

L

(c) LVTTL Input Test Waveform

(d) CML/LVPECL Input Test Waveform

≤ 1 ns

≤ 1 ns

V

IHE

V

ILE

V

IHE

V

ILE

[12]

[12]