5 technical specification, Technical specification - 10, Introduction am5010 – Kontron AM5010 User Manual

Page 28

Introduction

AM5010

Page 1 - 10

ID 1022-1107, Rev. 4.0

P R E L I M I N A R Y

1.5

Technical Specification

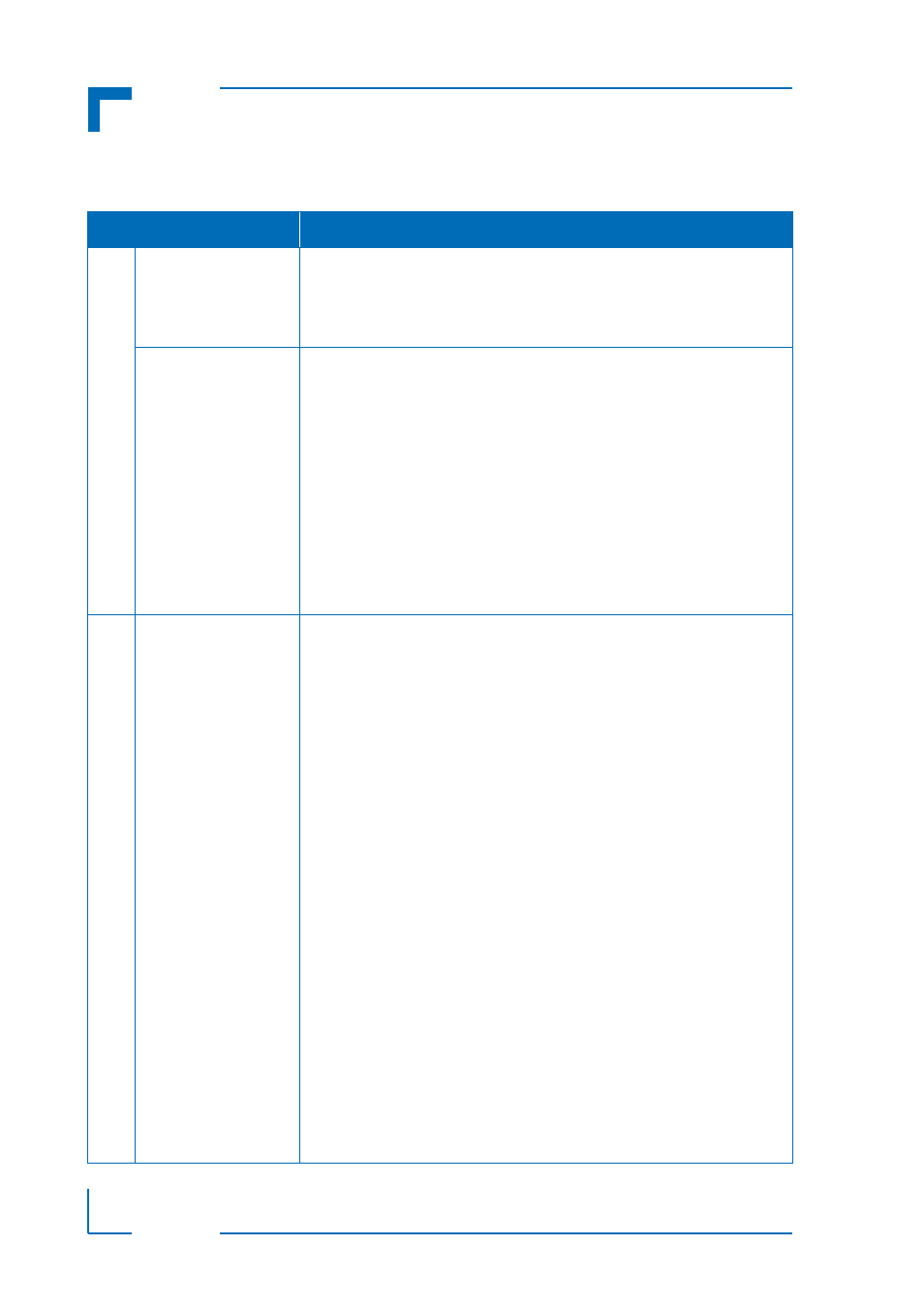

Table 1-2:

AM5010 Main Specifications

FEATURES

SPECIFICATIONS

Processor and Memory

CPU

The AM5010 supports the following microprocessor:

•

Intel® Core™2 Duo processor L7400 (LV), 1.5 GHz, 667 MHz FSB,

4 MB L2 cache, 479 µFCBGA packaging

Please contact Kontron for further information concerning the suitability of

other Intel processors for use with the AM5010.

Memory

Main Memory:

•

Up to 4 GB registered DDR2 SDRAM memory with ECC running at

400 MHz (PC3200)

Cache structure:

•

64 kB L1 on-die full speed processor cache

•

32 kB for instruction cache

•

32 kB for data cache

•

4 MB L2 on-die full speed processor cache

FLASH Memory:

•

Two redundant Firmware Hub (FWH) Flash chips (2 x 1 MB) controlled

by the MMC

Mass Storage Device:

•

Up to 8 GB USB 2.0 NAND Flash memory optionally available

Serial EEPROM with 64 kbit

Chips

et

Intel® 3100

Intel® 3100 chipset:

•

Support for a Core™2 Duo processor

•

64-bit AGTL/AGTL+ based System Bus interface at up to 667 MHz

•

System Memory interface with optimized support for DDR2 SDRAM

memory at 400 MHz with ECC

•

Three x4 PCI Express ports

•

RASUM (Reliability, Availability, Serviceability, Usability, and Manage-

ability) features:

•

Memory error detection and reporting of 1- and 2-bit errors including

correction of 1-bit failures

•

Integrated Memory Scrub Engine, which logs any uncorrectable

memory errors

•

Support for automatic read retry on uncorrectable errors

•

Memory sparing allows for one memory bank per channel to be held

in reserve and brought on-line if another memory bank in the chan-

nel becomes defective (only supported with 2 GB main memory con-

figuration)

•

Six-Channel SATA 150 interface (only three channels are used)

•

USB 2.0 host interface with up to four USB ports available (only three

USB 2.0 ports are used on the AM5010)

•

Firmware Hub (FWH) interface support

•

Low Pin Count (LPC) interface

•

PCI Rev. 2.2 compliant with support for 32-bit/33 MHz PCI operations

(not used on the AM5010)

•

Power management logic support

•

Enhanced DMA controller, interrupt controller, and timer functions

•

System Management Bus (SMBus) compatible with most I²C™ devices

•

Two 16550-compatible Serial ports (COM)

•

Battery backed-up real-time clock (RTC)