Kontron AM4211 User Manual

Page 77

C-2

www.kontron.com

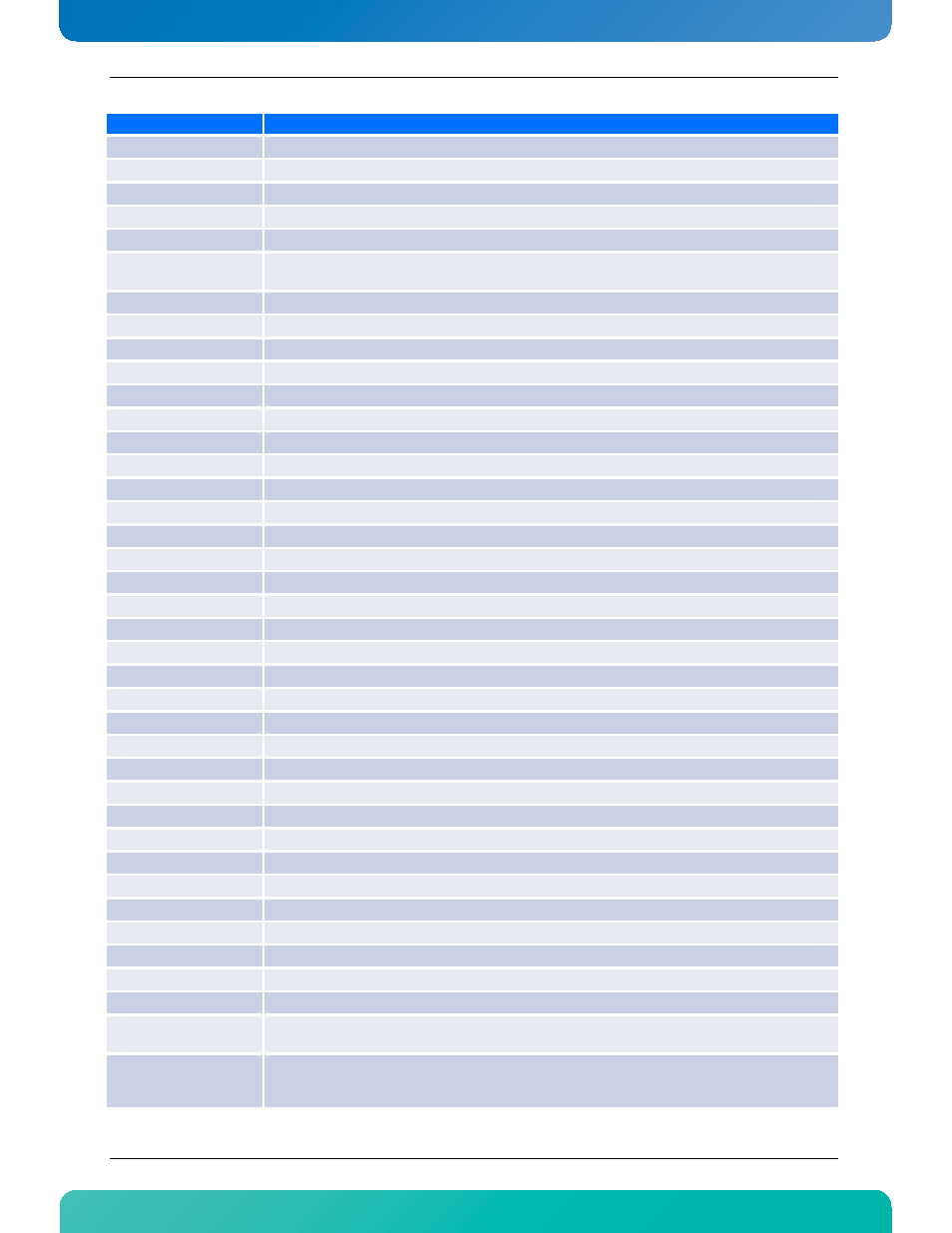

CRC

Cyclic Redundancy Check

CS1

Components Side 1 as describes in PICMG3.0.

CS2

Components Side 2 as describes in PICMG3.0.

CTCA

Compact Telecom Computing Architecture

CTS

Clear To Send

DDR2

(Same as DDR-II). DDR2 SDRAM or Double-Data-Rate two (2) Synchronous Dynamic Random Access

Memory.

DHCP

Dynamic Host Configuration Protocol

DIMM

Dual In-line Memory Module

DIN

Deutsches Institut für Normung. German Institute for Standardization.

DMA

Direct Memory Access

DMI

Desktop Management Interface

DPLL

Digital Phase-Locked Loop

DRAM

Dynamic Random Access Memory

DTC

Data Transfer Controller

DTR

Data Terminal Ready

DTS

Digital Thermal Sensor in IA32 processors.

ECC

Error Checking and Correction

EEPROM

Electrically Erasable Programmable Read-Only Memory

EFI

Extensible Firmware Interface

EFT

Electric Fast Transient

EHCI

Enhanced Host Controller Interface. Specification for Universal Serial Bus specification, revision 2.0.

EIA

Electronic Industries Alliance

EISA

Extended Industry Standard Architecture. Superset of ISA, 32-bit bus architecture.

EIST

(Same as SpeedStep). Enhanced Intel SpeedStep Technology

EMC

ElectroMagnetic Compatibility

EMI

ElectroMagnetic Interference

EMTTM

Turbo mode and enhanced Multi Threaded Thermal Management

ERM

Electromagnetic compatibility and Radio spectrum Matters

ESD

ElectroStatic Discharge

ETH

Same as Ethernet.

ETSI

European Telecommunications Standards Institute

FADT

Fixed ACPI Description Table

FC

Fibre Channel

FC-AL

Fibre Channel-Arbitrated Loop

FI

Fabric Interface. Backplane connectivity defined by the ATCA.

FML

Fast Management Link

FPGA

Field-Programmable Gate Array

FPL

FPGA-to-PLD Link. FPL is a 20 MHz serial link that exchange 32-bit of data in each direction between

the FPGA and a companion PLD. Comes from Kontron Canada.

FRBx

Fault-Resilient Booting level [1-3]. A term used to describe system features and algorithms that

improve the likelihood of the detection of, and recovery from, processor failures in a multiprocessor

system.

Acronyms

Descriptions