1 power on self test, Power on self test - 8, Post routines and error codes - 8 – Kontron AT8901M User Manual

Page 58: At8901m software description

AT8901M

Software Description

Page 4 - 8

AT8901M User Guide

4.3.1

Power On Self Test

4.3.1.1

Test Routines

Upon power on or system reset, the bootloader performs a set of Power On Self Tests (POST)

to check the integrity of specific components. Components where a POST is available are:

• SDRAM

• PPC405 serial line

• PPC405 I2C

• PPC405 FE

In the case that a POST fails, a POST error code is written into the postcode high byte register

of the onboard CPLD. The boot process is not stopped as there are good chances the board

can boot even in case of POST errors. The postcode high byte register is also accessible by

the IPMC which can report error codes to a separate management instance. Thus more com-

prehensive diagnostic tests could be started.

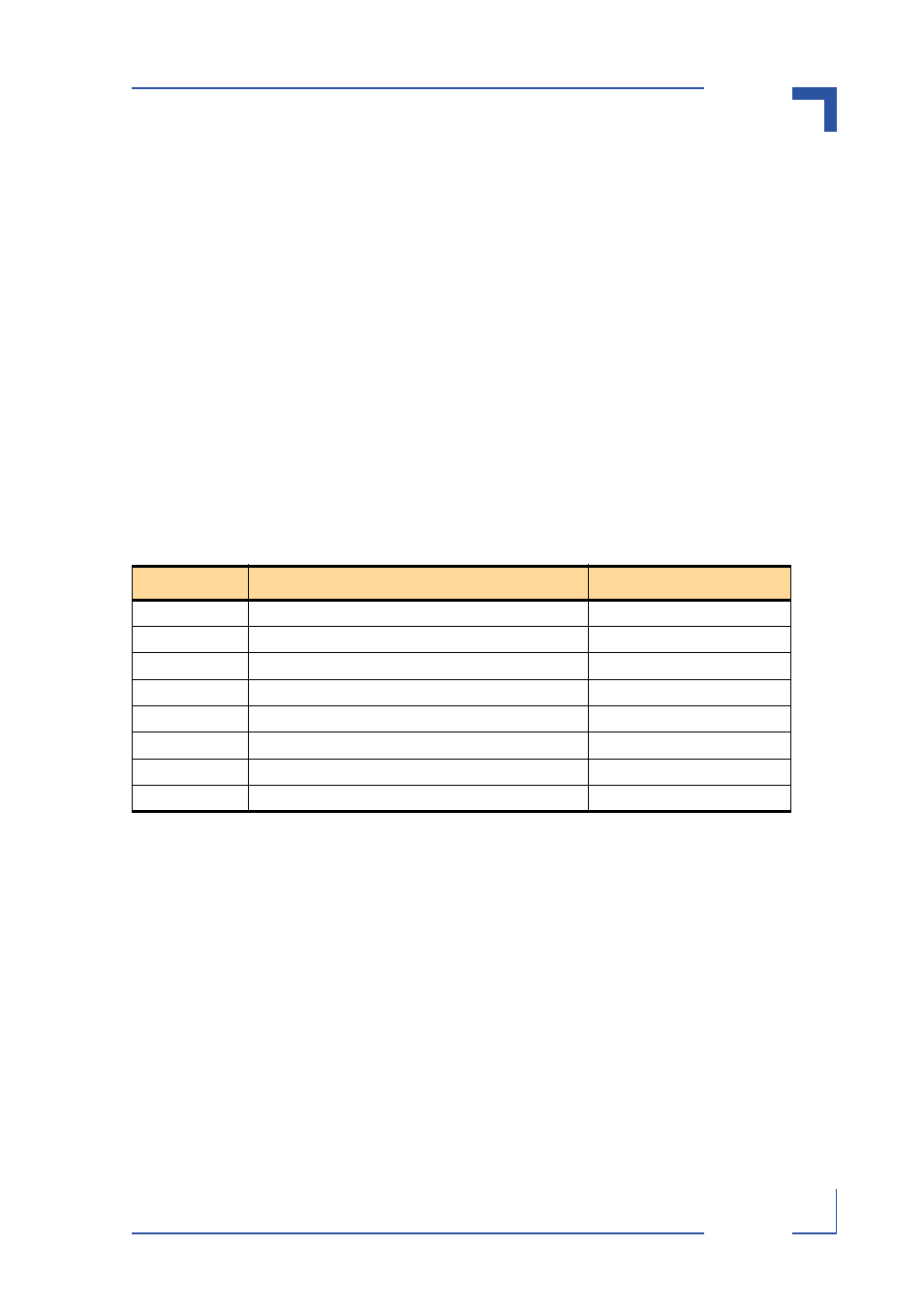

The following table shows a list of available POST routines including POST error codes.

4.3.1.2

Boot Steps

In addition to the Power On Self Tests described above, the bootloader logs the board startup

sequence in the postcode low byte register. A postcode value is written each time a step in the

start sequence has been completed successfully. The postcode stored is also accessible by

the IPMC. In the case that an error occurs during execution of a step, the boot sequence is

stopped because a fatal error has occurred with great likelihood. In this case, a management

instance can read the last postcode written via the IPMC and thus determine where the fatal

error has occurred.

Table 4-1: POST routines and error codes

Device

Test

POST Error Code

SDRAM

Data bus - walking 1 test

PCW_DLINE

SDRAM

Address bus - walking 1 test

PCW_ALINE

SDRAM

Memory - read/write test

PCW_MEM

PPC405 UART

Serial loopback teststring

PCW_SERIAL

PPC405 I2C

Bus scan for devices from I2C_ADDR_LIST

PCW_I2C

PPC405 FE

Phy access

PCW_ETH1

PPC405 FE

Phy loopback test using special Ethernet test frame

PCW_ETH2

KCS

KCS READY signal test

KCSCTL