Test bed and applications, Figure 3 – Dell PowerEdge R820 User Manual

Page 9

Performance Analysis of HPC Applications on Several Dell PowerEdge 12

th

Generation Servers

9

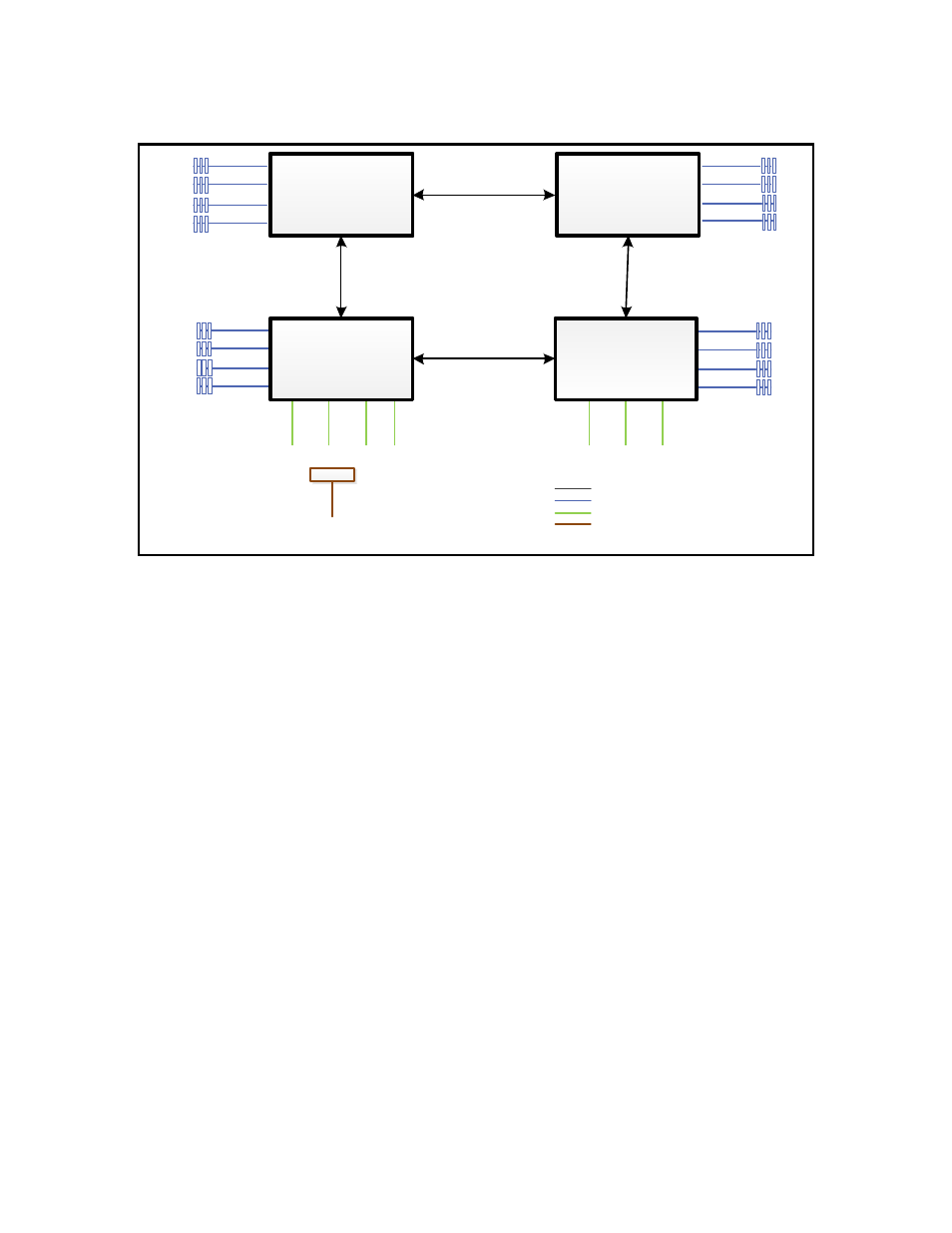

Platform architecture for Sandy Bridge EP - 4 Socket (Intel Xeon E5-4600)

Figure 3.

QPI links

8GT/s*2 bi-directional * 16b

1*32GB/s

1600MHz * 64b * 4

channels

51.2GB/s

51.2GB/s

x8

8GB/s

QPI

DDR3 memory channel

PCI-Gen3 lanes

Processor 1

Processor 0

PCI-E Gen3

8GT/s*128b/130b

FDR

56Gbps * 64b/66b * 2 bi-

directional=

13.6GB/s

InfiniBand

P

Processor 2

NDC

x8

Left

x16

Storage

x8

Right

x16

Right

x8

Center

x16

Processor 3

Information regarding any of the Intel Sandy Bridge processors can be obtained from [3].

3. Test bed and applications

The previous section presented the differences between the three Sandy Bridge based architectures.

This section details the test bed used in the study, explains the choices selected in configuring the test

bed, and describes the HPC applications used in this study. Subsequent sections evaluate the

performance of these HPC workloads on the different architectures.

Three types of HPC clusters were configured for this purpose. The details of this test bed are provided

in Table 2. A 16 server Dell PowerEdge M620 cluster was deployed to represent Sandy Bridge-EP while a

32 server PowerEdge M420 cluster represented the Sandy Bridge-EN. A four server PowerEdge R820

cluster was used for Sandy Bridge-EP 4S. A PowerEdge R620 rack server was used as the master node of

the cluster.