Figure 1, Figure 2 – Dell PowerEdge R820 User Manual

Page 8

Performance Analysis of HPC Applications on Several Dell PowerEdge 12

th

Generation Servers

8

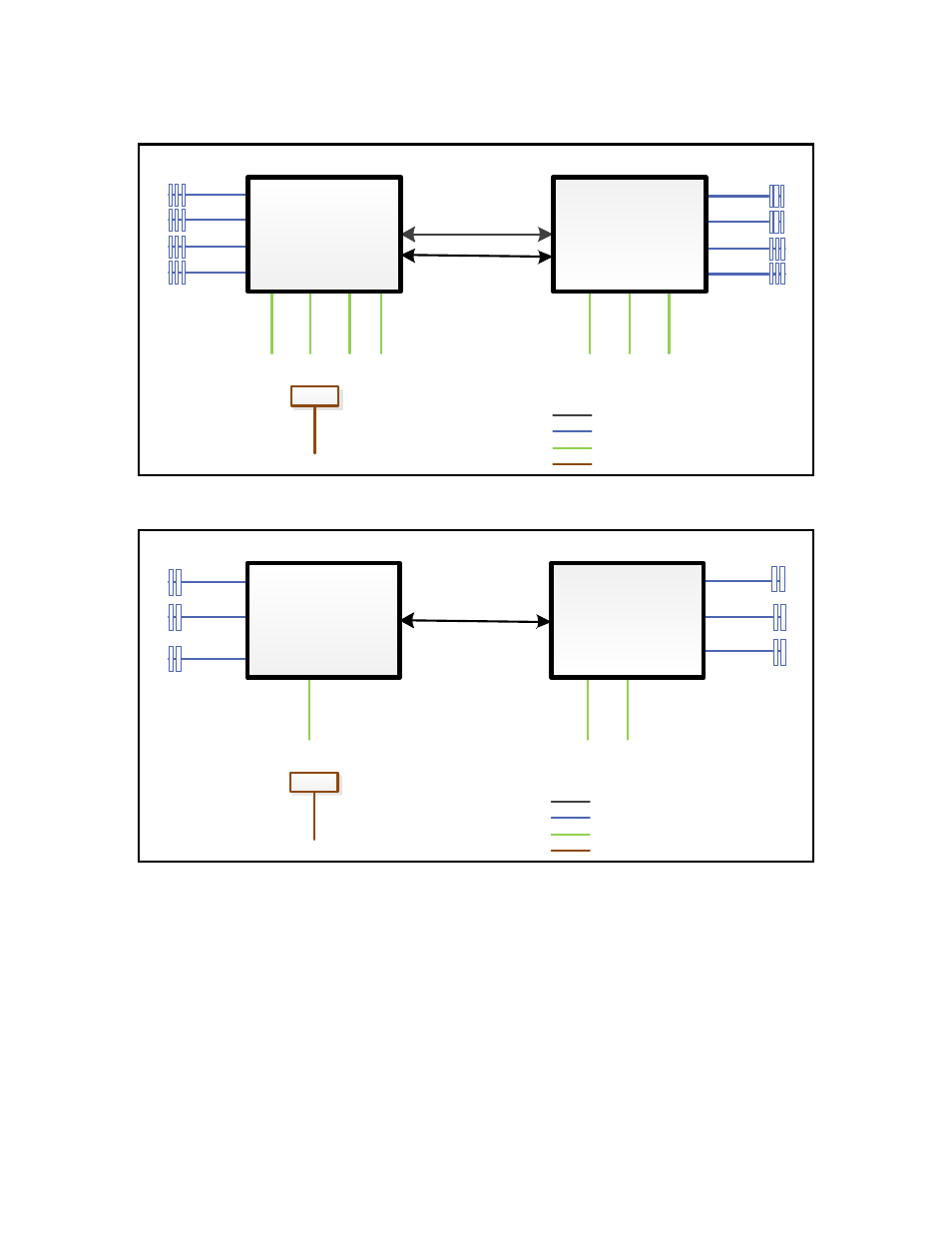

Platform architecture for Sandy Bridge EP (Intel Xeon E5-2600)

Figure 1.

QPI links

8GT/s*2 bi-directional

* 16b

2*32GB/s

1600MHz * 64b

* 4 channels

1600MHz

51.2GB/s

51.2GB/s

x8

8GB/s

QPI

DDR3 memory channel

PCI-Gen3 lanes

Processor

Processor

PCI-E Gen3

8GT/s*128b/130b

FDR

56Gbps * 64b/66b *

2 bi-directional=

13.6GB/s

InfiniBand

Left

x16

NDC

x8

Storage

x8

Right

x16

Right

x8

Center

x16

Platform architecture for Sandy Bridge EN (Intel Xeon E5-2400)

Figure 2.

QPI links

8GT/s*2 bi-directional

* 16b

1*32GB/s

1600MHz * 64b

* 3 channels

1600MHz

38.4GB/s

38.4GB/s

Left x16

16GB/s

QPI

DDR3 memory channel

PCI-Gen3 lanes

Processor

Processor

PCI-E Gen3

8GT/s*128b/130b

FDR10

50Gbps * 64b/66b *

2 bi-directional=

12.1GB/s

InfiniBand

Right x16

x8

Internal

PERC

Figure 3 describes the platform architecture of Sandy Bridge-EP 4 socket platform. Each socket has two

QPI links, but any two adjacent sockets are connected by just one QPI link in a ring-structure. There is

no cross link between processors one and three, and between processors zero and two. Thus, any

communication between these two socket pairs needs to traverse two QPI links. Only two of the

sockets have PCI-lanes and therefore can be local to PCI cards installed in the system. Other than the

differences in number of QPI links, the 4 socket platform architecture is very close to the 2 socket EP

platform architecture.