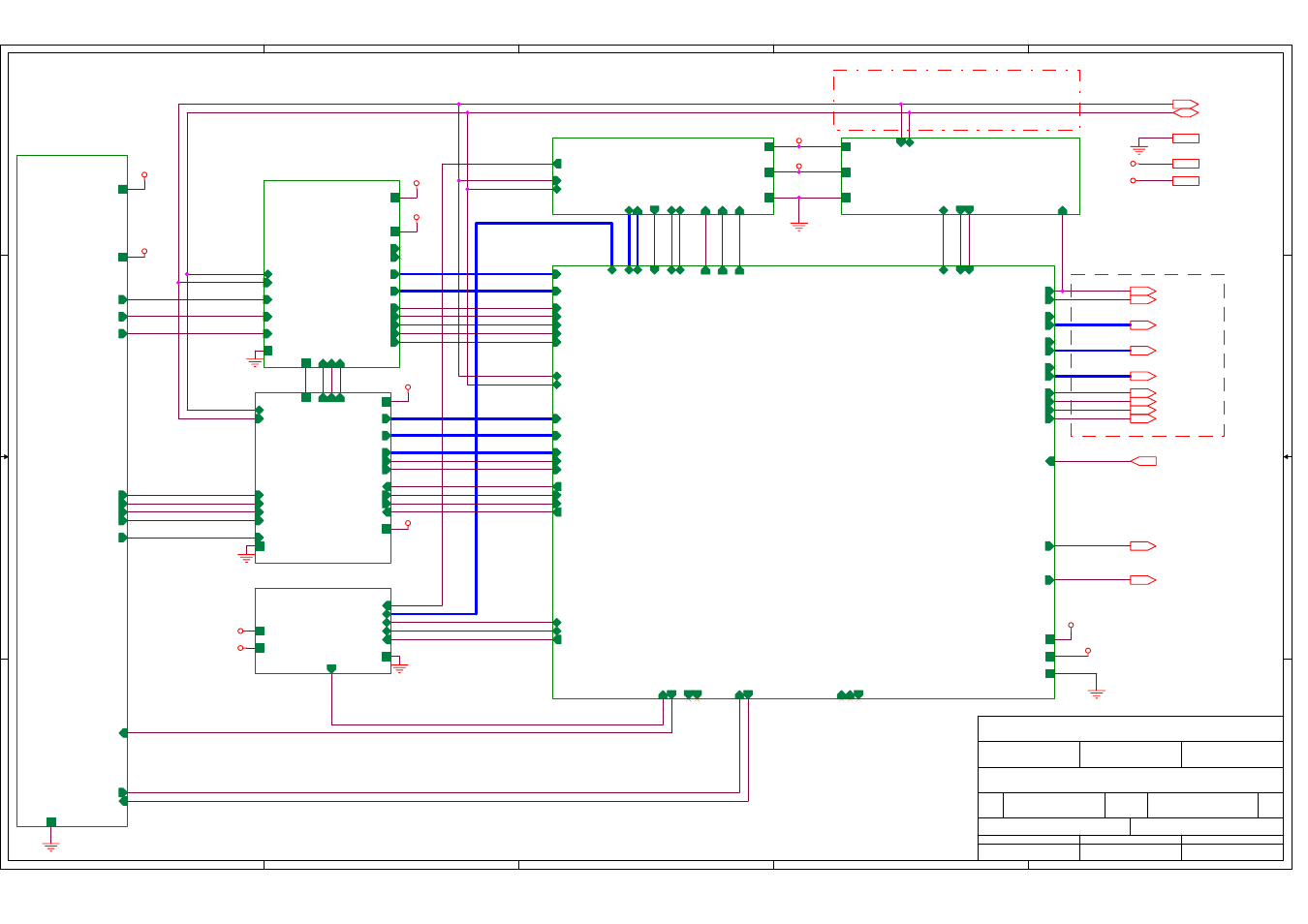

Benq corporation – BenQ PB6200 User Manual

Page 104

A

A

B

B

C

C

D

D

E

E

4

4

3

3

2

2

1

1

SCL

POWE

R

O

N

GGE[7:0]

GGE[7:0]

CS0n

CS0n

A0

ROMWEn

DVS

ECO-MODE

B

HENn

RESET

A[19:1]

D EN

GVS

GVS

DCKEX

T

GRE[7:0]

GRE[7:0]

SDA

DGE[7:0]

DBE[7:0]

RESETZ

DCLK

GCOAST

GCOAST

GFBK

GFBK

LAMPLITZ

FAN_P

GBE[7:0]

GBE[7:0]

GCLK

GCLK

GBLKSPL

GBLKSPL

CS1n

CS1n

ROMOEn

D[0:1

5

]

GHS

GHS

VPPEN

D HS

POWERON

K

E

YSTONE

DRE[7:0]

M

C

KEXT

SDA

IRR

C

V

R

IRR CVR

GAIN_C

GAIN_C

BAIN_C

BAIN_C

CONTROL

HSYNC

HSYNC

RAIN_C

RAIN_C

TXD

TXD

VSYNC_C

VSYNC_C

RXD

RXD

VHS

VHS

CVBS

CVBS

GAI

N

_

V

VVS

VVS

VY[7:0]

VY[7:0]

BAI

N

_

V

CHROMA

CHROMA

SDA

LUMA

LUMA

VUV[7:0]

VUV[7:0]

VCLK

VCLK

VFIELD

VFIELD

VPEN

VPEN

RAI

N

_

V

AVDD

SCL

RESETn

SCL

SDA

SCL

D[0:7]

D

[0:7]

3.3V

VDD

SCL

SDA

GND

POWERON

DEN

RESETZ

LAMPLITZ

DGE[7:0]

DHS

DRE[7:0]

DCLK

DVS

DBE[7:0]

ECO-MODE

FAN_P

VDD

3.3V

VDD

VDD

3.3V

VDD

3.3V

3.3V

VDD

3.3V

VDD

V33

VDD

V33

Title

Size

Document Number

R ev.

Date:

Sheet

o f

Project Code

Reviewed By

Approved By

Prepared By

Model Name

PCB P/N

PCB Rev.

Benq Corporation

OEM/ODM Model Name

48.J8601.S04

MAIN BOARD

2

20

DAVID HN LIN

KELVIN LIAO

99.J8677.B12-C3-304-004

S04

ANGEL HU

PB6100

99.J8677.001

1

Tuesday, October 07, 2003

Note: To DDP1000 input port

Note: Lamp on/off detect signal.

Note: PW164B RS232 I/O port connect with

PC ( for control ) and Ballast ( for lamp

stasus )

Regect RC1 and RC2 before connect DX660 main board with

INTERFACE board.

PAGE_10

015_PW166

VCLK

VFIELD

VVS

VHS

VPEN

VY[7:0]

GGE[7:0]

GRE[7:0]

GVS

GBLKSPL

GHS

GFBK

GCLK

GBE[7:0]

GCOAST

TDO

TXD

ROMWEn

TCK

RXD

MCKEXT

ROMOEn

IRRCVR

TMS

A[19:1]

DCKEXT

RESET

D[0:15]

SDA

DVS

DHS

DRE[7:0]

DCLK

DGE[7:0]

DBE[7:0]

A0

BHENn

DEN

VUV[7:0]

POWERON

RESETZ

DRO[7:0]

DGO[7:0]

DBO[7:0]

SCL

VPPEN

AUDIO_MUT

3.3V

CS0n

LAMPLITZ

GND

ECO-MODE

KEYSTONE

AUDIO_VOL

CS1n

FAN_P

VDD

D[0:7]

CONTROL

key8

DECODE

012_DECODE

VDD

VUV[7:0]

SCL

SDA

V33

VY[7:0]

VHS

VVS

VPEN

CVBS

VCLK

VFILD

LLC1

LLC2

LUMA

CHROMA

GAIN_V

RAIN_V

BAIN_V

AVDD

GND

PAGE_12

017_KEY

D[0:7]

CS0n

VDD

3.3V

GND

CS1n

RESETn

IRRCVR

key8

PAGE_11

016_MISC

POWERON

DCKEXT

MCKEXT

VDD

3.3V

GND

KEYSTONE

SDA

SCL

PAGE_8

013_AFE

SCL

SDA

GBLKSPL

GCOAST

HSYNC

GBE[7:0]

GGE[7:0]

GRE[7:0]

GFBK

GHS

GVS

GCLK

VDD

GND

RAIN_C

GAIN_C

BAIN_C

VSYNC_C

RAIN_V

GAIN_V

BAIN_V

AVDD

V33

INPUT

011_INPUT

RXD

TXD

HSYNC

BAIN_C

RAIN_C

GAIN_C

VSYNC_C

CONTROL

VDD

3.3V

GND

CVBS

LUMA

CHROMA

PAGE_9

014_MEMORY&KEYSTONE

VPPEN

A[19:1]

D[0:15]

3.3V

GND

ROMWEn

ROMOEn

SCL

SDA

A0

BHENn

RESET

RESETn

VDD