4 clocking, 5 clock and data headers, 6 cpld board setup – Cirrus Logic CDB8421 User Manual

Page 4: Cdb8421

CDB8421

4

DS641DB3

1.4

Clocking

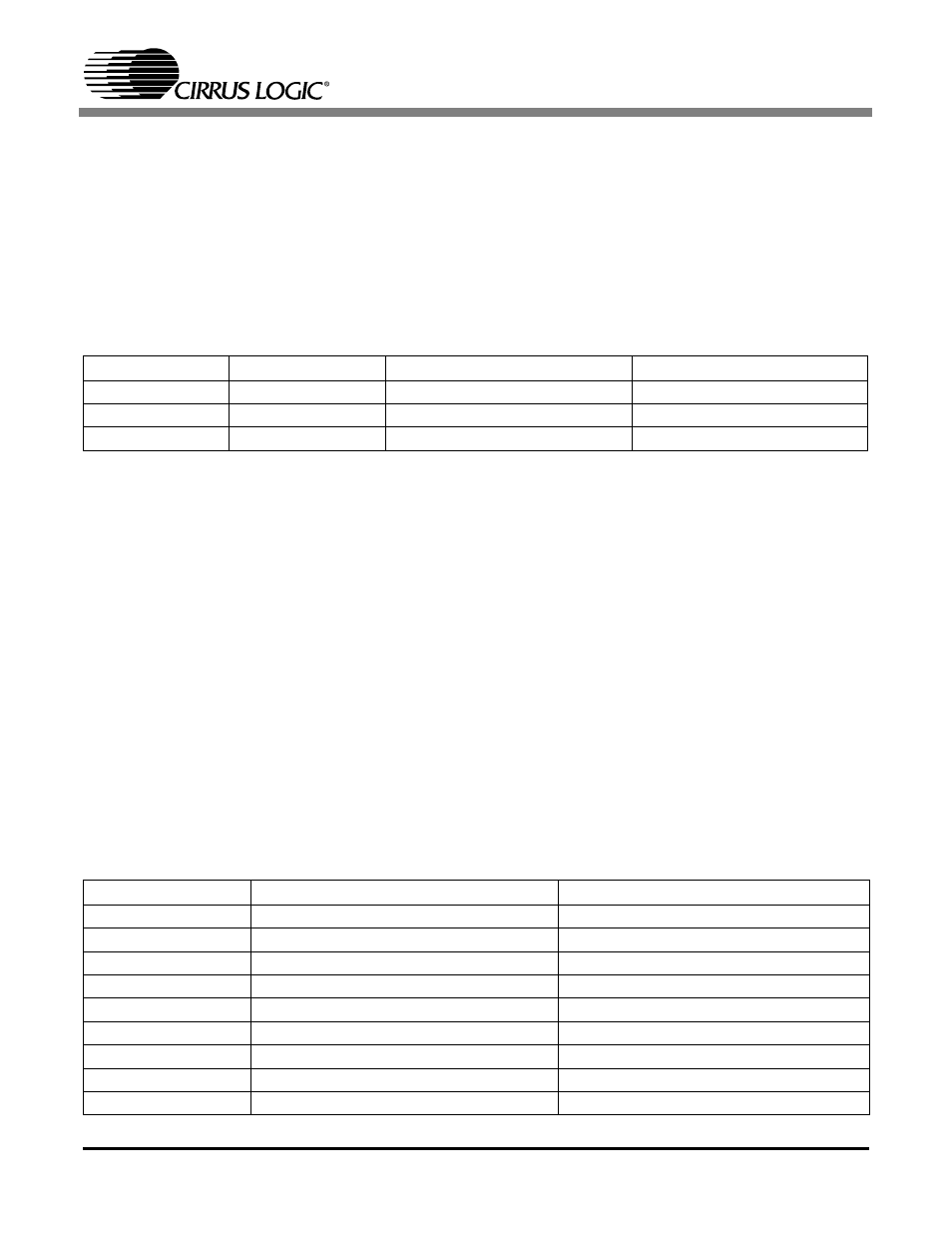

Table 1 shows the available I/O configurations and their respective clock sources. When the

CS8416 is selected to master SCLK and LRCK (CS8421 input port set to slave), J7 should

be set to 8416. When the CS8421 input port is selected to master SCLK and LRCK (CS8416

set to slave), J7 may be set to 8416, OSC, or XTAL. When the CS8406 is selected to master

SCLK and LRCK (CS8421 output port set to slave), J13 should be set to OSC. When the

CS8421 output port is selected to master SCLK and LRCK (CS8406 set to slave), J13 should

be set to 8421. The board is shipped with a 24.576 MHz crystal/oscillator stuffed at Y1, Y2,

and Y3.

1.5

Clock and Data Headers

The CDB8421 includes headers for input (J8) and output (J11) port clocks and data. These

headers can enabled/disabled using S4. When not using these headers, SDIN should be

jumpered to SDOUT on both J8 and J11. The pin functions for headers J8 and J11 are shown

in Table 7.

The CDB8421 also includes a header for TDM operation (J16). Refer to the CS8421 data

sheet for possible TDM configurations [1]. This header can enabled/disabled using J14.

All headers operate at the VL supply, therefore any external circuit connected to these head-

ers should also operate at VL.

1.6

CPLD Board Setup

The CPLD (U2) controls all of the configuration for the CS8421, CS8416, and CS8406. The

CPLD decodes switches S1, S2, S3, and S4 and sets the appropriate mode of operation.

Switch S1 controls the master/slave and MCLK/LRCK ratio settings for the CS8421, CS8416,

and CS8406. The functions for S1[3:0] are detailed in Table 2.

CS8421 Input Port CS8421 Output Port

CS8421 XTI/XTO Clock Source

CS8406 OMCK Clock Source

Master

Slave

CS8416 RMCK

Y3

Slave

Master

CS8416 RMCK, Y1, or Y2

CS8421 MCLK_OUT

Slave

Slave

CS8416 RMCK, Y1, or Y2

Y3

Table 1. Clock Sources

S1[3:0]

CS8421 Input

CS8421 Output

0000

Slave

Slave

0001

Slave

Master (Master Clock = 128*Fs)

0010

Slave

Master (Master Clock = 256*Fs)

0011

Slave

Master (Master Clock = 384*Fs)

0100

Slave

Master (Master Clock = 512*Fs)

1000

Master (Master Clock = 128*Fs)

Slave

1001

Master (Master Clock = 256*Fs)

Slave

1010

Master (Master Clock = 384*Fs)

Slave

1011

Master (Master Clock = 512*Fs)

Slave

Table 2. Switch S1, Serial Input and Output Master/Slave and Speed Mode Settings