7 ain & vref sampling structures, 8 converter performance, Cs5571 – Cirrus Logic CS5571 User Manual

Page 20

CS5571

20

DS768PP1

3/25/08

10:56

3.7 AIN & VREF Sampling Structures

The CS5571 uses on-chip buffers on the AIN and VREF+ inputs. Buffers provide much higher input im-

pedance and therefore reduce the amount of drive current required from an external source. This helps

minimize errors.

The Buffer Enable (BUFEN) pin determines if the on-chip buffers are used or not. If the BUFEN pin is

connected to the V1+ supply, the buffers will be enabled. If the BUFEN pin is connected to the V1- pin,

the buffers are off. The converter will consume about 30 mW less power when the buffers are off, but the

input impedances of AIN, ACOM and VREF+ will be significantly less than with the buffers enabled.

3.8 Converter Performance

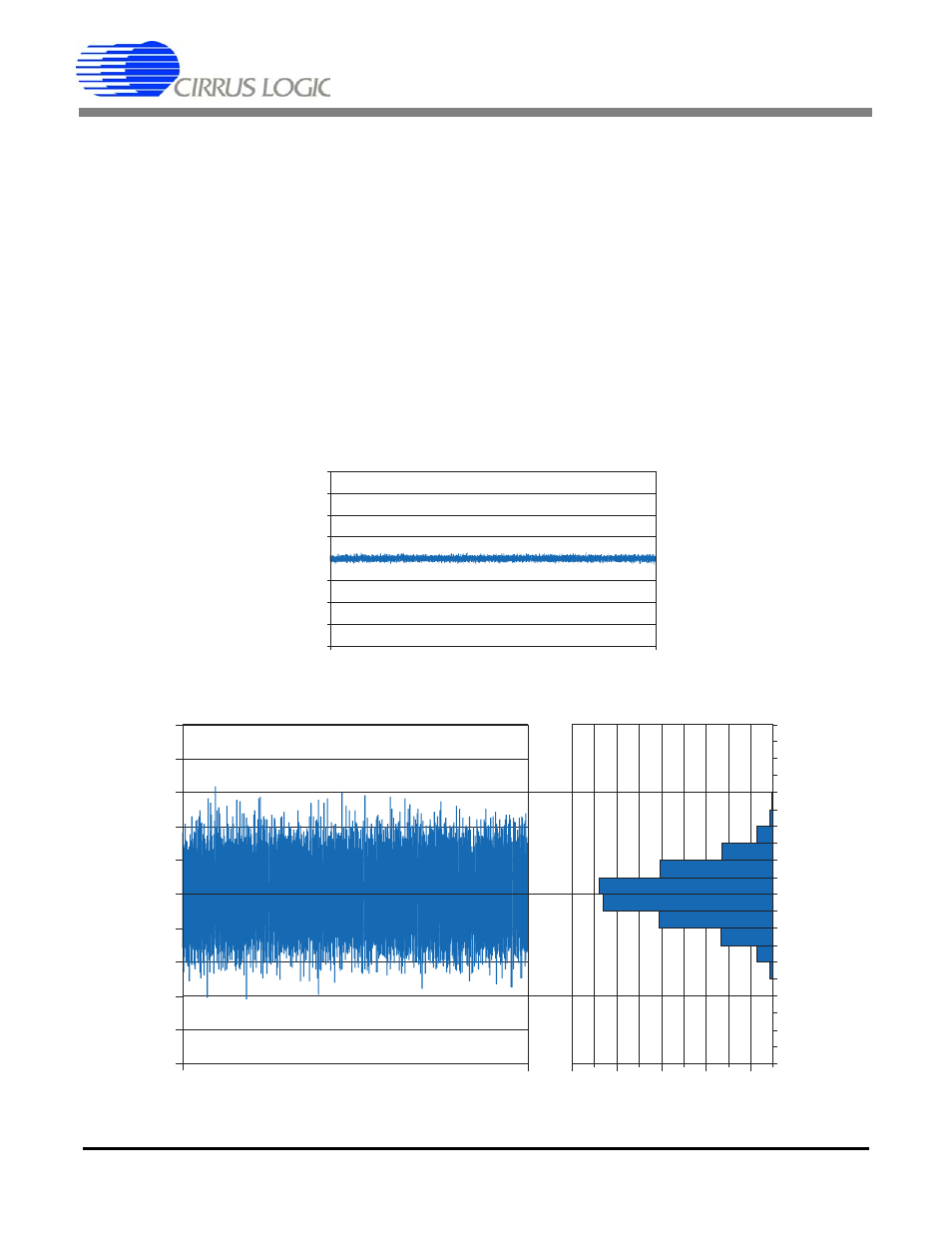

The CS5571 achieves excellent differential nonlinearity (DNL) as shown in figures 9 and 10. Figure 9 il-

lustrates the code widths on a typical scale of ±1 LSB. Figure 10 illustrates a zoom view of figure 9 on a

scale of ±0.1 LSB. Figure 10 also includes a DNL error histogram that indicates that the errors are equally

distributed about the perfect code size; and most codes are accurate within ±0.01 LSB.

Figure 9. CS5571 DNL Plot

Figure 10. CS5581 DNL Error Plot with DNL Histogram

-1.00

-0.75

-0.50

-0.25

0.00

0.25

0.50

0.75

1.00

1

65535

DNL

Error

in

L

SBs

Codes

2k

4k

6k

8k

10k

12k

14k

16k

18k

0

0

+0.08

+0.07

+0.06

+0.05

+0.04

+0.03

+0.02

+0.01

-0.01

-0.02

-0.03

-0.04

-0.05

-0.06

-0.07

-0.08

-0.09

-0.1

+0.09

+0.1

DNL

Error

in

L

SBs

Counts per 0.01 LSB Error

-0.10

-0.08

-0.06

-0.04

-0.02

0

+0.02

+0.04

+0.06

+0.08

+0.10

1

65535

Codes

DNL

Error

in

L

SBs