Cirrus Logic AN44 User Manual

Page 6

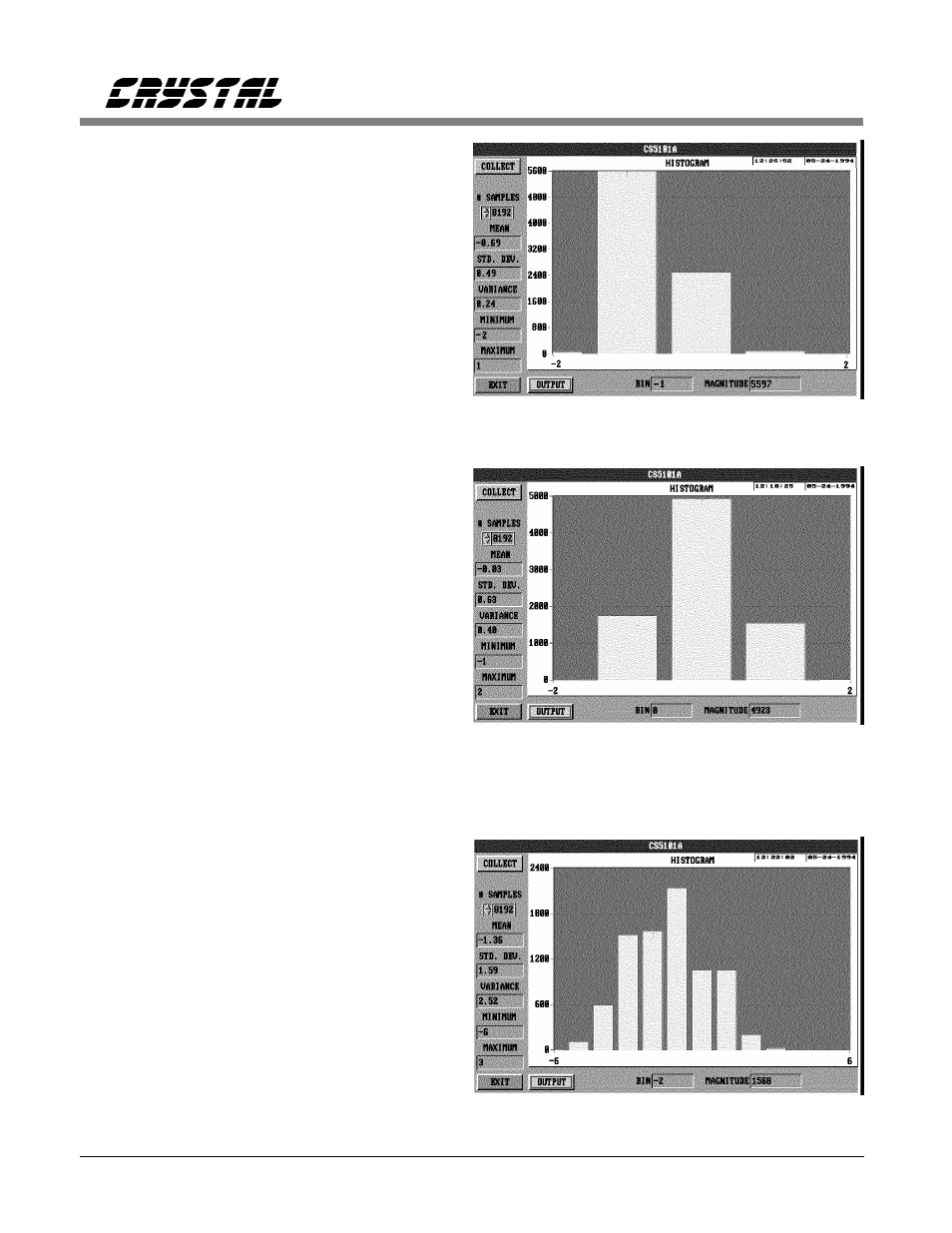

Testing An Embedded ADC

System performance can be measured by

interfacing the embedded ADC. The previous

sections described the hardware modification

required to interface a Crystal Semiconductor

ADC with the CAPTURE board. Figures 8, 9,

and 10 are the results of using the histogram test

on a CS5101A in an embedded system.

Figure 8 is a histogram of a CS5101A operating

in the bipolar mode with the analog input pin

grounded right at the package. Data book

performance is expected, if proper design

practices have been used in developing the

circuit and layout. In Figure 8, the mean is -0.69

counts, which is well within the typical

specification of two counts for the bipolar offset.

The standard deviation is 0.49 counts. This

translates to 67 uV

RMS

(

0.49 x 9 volts

⁄

2

16

)

. The

CS5101A data sheet specifies 70 uV

RMS typical.

A buffer op-amp is integrated in the system and

a data set is collected and displayed in Figure 9.

Both the mean and standard deviation numbers

changed with the addition of the op-amp. The

op-amp added 0.66 counts to the offset or

91 uV. The RMS noise increased to 0.63 counts

or 87 uV.

Figure 10 shows the histogram for the ADC,

buffer op-amp, and signal source. The signal

source output is set at zero volts. The histogram

statistics indicate an offset of 1.59 counts or 218

uV and the RMS noise is at 218 uV. Note, that

as more components are added to the system, the

offset changes and the noise increases. These

changes can be used to isolate and identify

problems.

Figure 9. Histogram of a CS5101A with a Buffer Op-Amp

Figure 10. Histogram of a CS5101A with a Signal Source

Figure 8. Histogram of a CS5101A with the Input

Grounded

Using The CDBCapture System with Embedded A/D Converters

6

AN44REV2