Digital characteristics (cont.), Cs5373a – Cirrus Logic CS5373A User Manual

Page 16

CS5373A

16

DS703F2

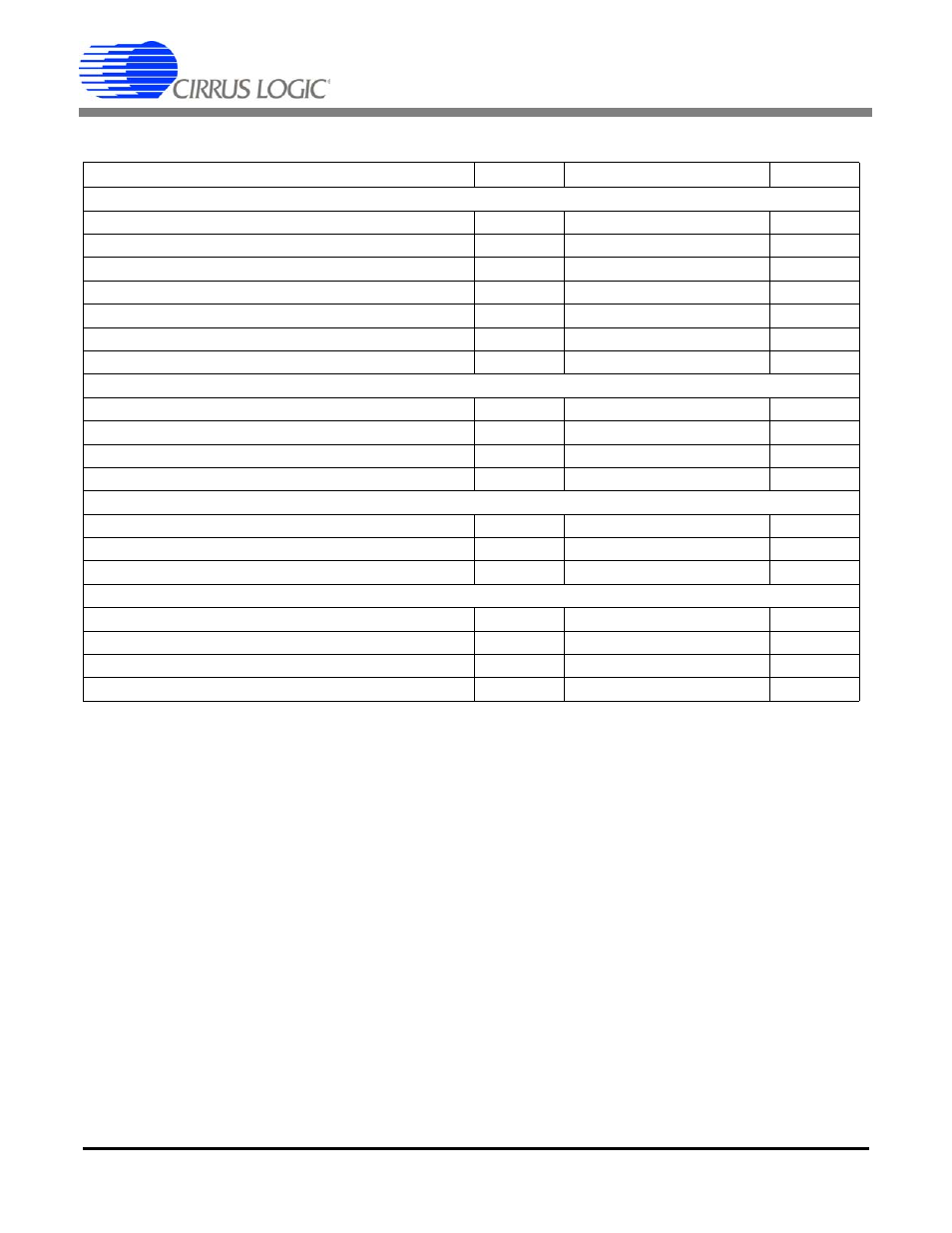

DIGITAL CHARACTERISTICS (CONT.)

Notes: 32. MCLK is generated by the CS5378 digital filter. If MCLK is disabled, the device automatically enters a

power-down state.

33. MSYNC is generated by the CS5378 digital filter and is latched on MCLK rising edge, synchronization

instant (t

0

) on next MCLK rising edge.

34. TDATA can be delayed from 0 to 63 full bit periods by the test bit stream generator in the CS5378 digital

filter. The timing diagrams show no TBSDATA delay.

35. Decimated, filtered, and offset corrected 24-bit output word from the CS5378 digital filter.

36. TDATA is generated by the test bit stream generator in the CS5378 digital filter.

37. TBSGAIN register value in the CS5378 digital filter.

Parameter

Symbol Min Typ

Max

Unit

Master Clock Input

MCLK Frequency

(

f

CLK

-

2.048

-

MHz

MCLK Period

(

t

mclk

-

488

-

ns

MCLK Duty Cycle

(

MCLK

DC

40

-

60

%

MCLK Rise Time

(

t

RISE

-

-

50

ns

MCLK Fall Time

(

t

FALL

-

-

50

ns

MCLK Jitter (In-band or aliased in-band)

(

MCLK

IBJ

-

-

300

ps

MCLK Jitter (Out-of-band)

(

) MCLK

OBJ

-

-

1

ns

Master Sync Input

MSYNC Setup Time to MCLK Rising

(

t

mss

20

122

-

ns

MSYNC Period

t

msync

40

976

-

ns

MSYNC Hold Time after MCLK Falling

(

t

msh

20

122

-

ns

MSYNC Instant to TDATA Start

(

t

tdata

-

1220

-

ns

MDATA Output

MDATA Output Bit Rate

f

mdata

-

512

-

kbits/s

MDATA Output One’s Density Range

(

MDAT

OD

14

-

86

%

Full-scale Output Code

(

MDAT

FS

0xA2EAAE

-

0x5D1C41

TDATA Input

TDATA Input Bit Rate

(

f

tdata

-

256

-

kbits/s

TDATA Input One’s Density Range

(

TBS

OD

25

-

75

%

TBSGAIN Full-scale Code

(

TBS

FS

-

0x04B8F2

-

TBSGAIN -20 dB Code

(

TBS

-20dB

-

0x0078E5

-