Cirrus Logic AN298 User Manual

Page 16

16

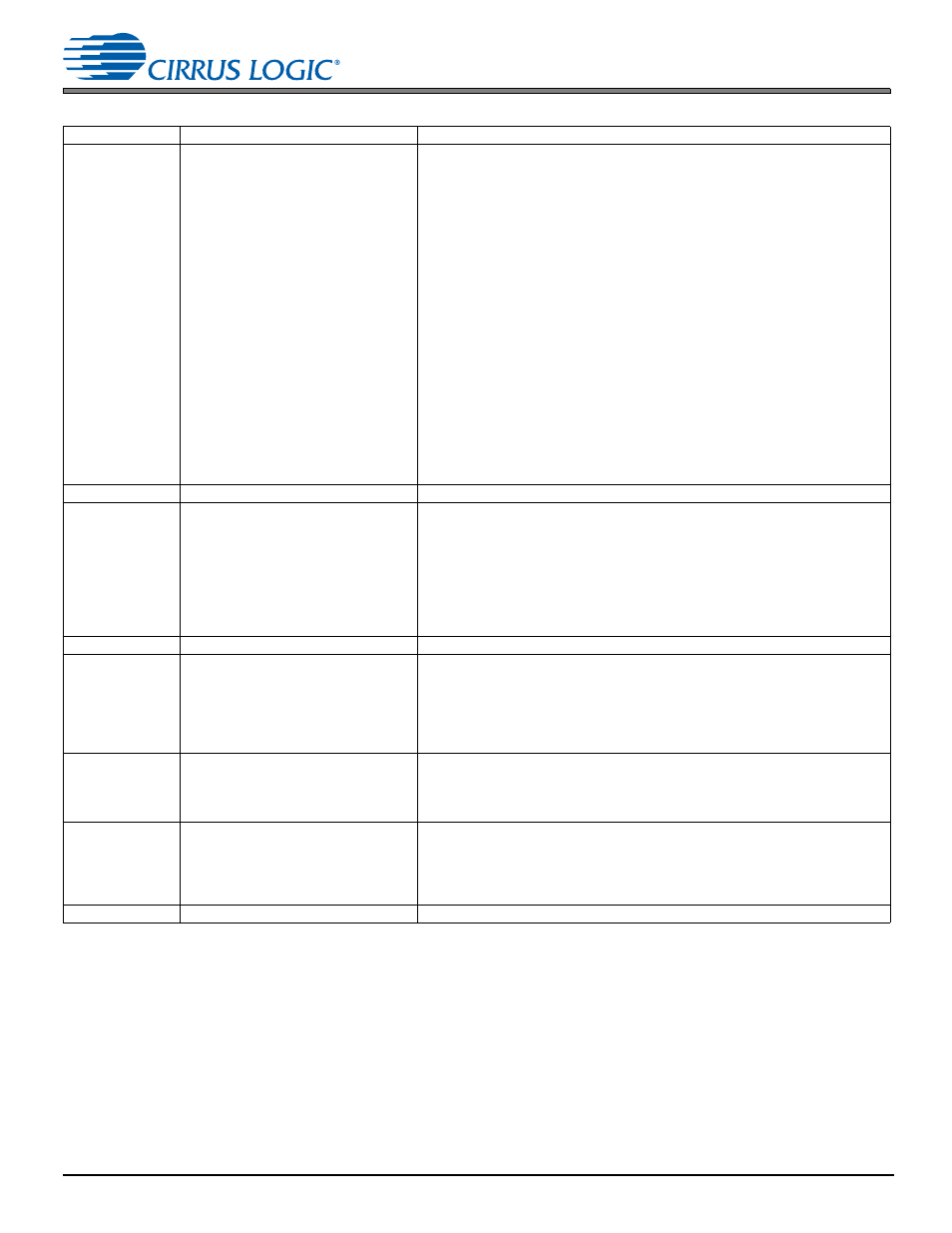

AN298RC14

4.2 OS Manager

0x0003

SAMPLE_RATE

†

Set by host

Bits 3:0 Sample Rate

0x0 = 48 kHz

0x1 = 44.1 kHz

0x2 = 32 kHz

0x3 =

0x4 = 96 kHz

0x5 = 88.2 kHz

0x6 = 64 kHz

0x7 =

0x8 = 24 kHz

0x9 = 22.05 kHz

0xA = 16 kHz

0xB =

0xC = 192 kHz

0xD = 176.4 kHz

0xE = 128 kHz

0xF =

Default = 0x00000000 (48kHz)

0x0004–0x0008

Reserved

Reserved

0x0009

SOFTBOOT

†

Bit 4: 1 = Engage Low Power Mode.

Bit 0: 0/1 disable/initiate soft boot sequence.

Once a soft boot is initiated, the OS will send a 0x00000005 (SOFT_BOOT_ACK)

to the host. The host can then use the standard boot protocol to download one or

more overlays. After a soft boot is initiated, the OS will respond to boot protocol

messages only.

The bit is reset to 0 after the soft boot is complete.

Default = 0x00000000

0x000A–0x003A

Reserved

Reserved

0x003B

GPIO_D

GPIO Data register.

Bits 31:0

Bit[i] corresponds to pin GPIO[i] (i = 0,...,31).

Note: Both the GPIO_OE and GPIO_MUX must be set to 1 for a particular bit

before that bit can be written. Bit 13

and

12 of KICKSTART variable must be set

to 1 (enabled).

0x003C

GPIO_OE

GPIO Data Direction register.

Bits 31:0

When Bit[i] is 1, pin GPIO[i] is configured as an output. When Bit[i] is 0, pin

GPIO[i] is configured as an input. (i = 0,...,31).

0x003D

GPIO_MUX

GPIO MUX Selector register.

Bits 31:0

When Bit[i] is 1, pin GPIO[i] is a GPIO function. When Bit[i] is 0, pin GPIO[i] is

overwritten by the other function on that pin. Also, when Bit[i] is 0, Bit[i] of the

GPIO_D register is not writable

0x003E–0x0043

Reserved

Reserved

Table 4-1. OS Module API (Cont.)

Index

Variable

Description