Cirrus Logic CS4384 User Manual

Cs4384, Features, Description

Copyright

© Cirrus Logic, Inc. 2008

(All Rights Reserved)

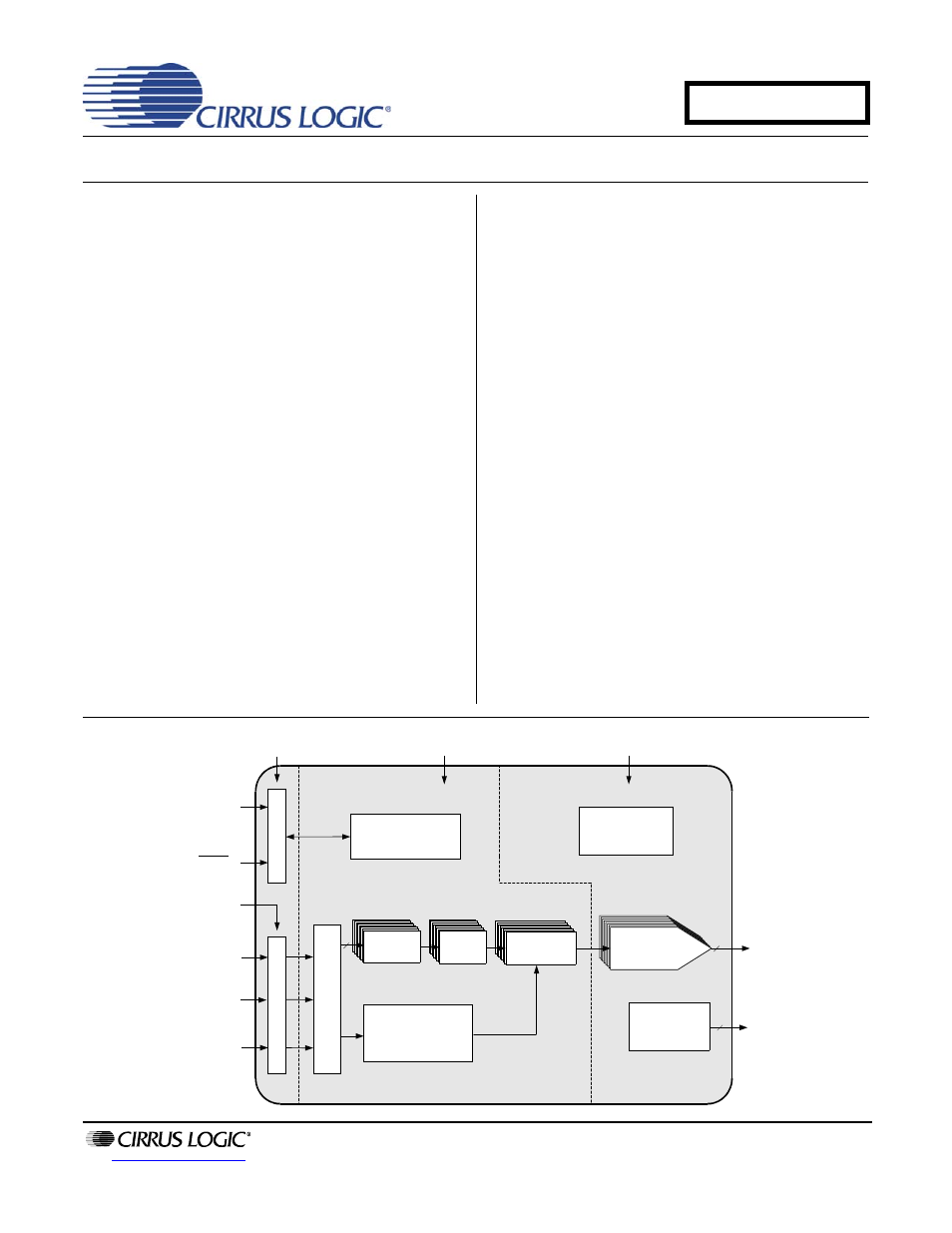

103 dB, 192 kHz 8-Channel D/A Converter

Features

Advanced Multi-bit Delta Sigma Architecture

24-bit Conversion

Automatic Detection of Sample Rates up to

192 kHz

103 dB Dynamic Range

-88 dB THD+N

Single-Ended Output Architecture

Direct Stream Digital

®

(DSD

™)

Mode

–

Non-Decimating Volume Control

–

On-Chip 50 kHz Filter

–

Matched PCM and DSD Analog Output

Levels

Compatible with Industry-Standard Time

Division Multiplexed (TDM) Serial Interface

Selectable Digital Filters

Volume Control with 1/2-dB Step Size and Soft

Ramp

Low Clock-Jitter Sensitivity

+5 V Analog Supply, +2.5 V Digital Supply

Separate 1.8 to 5 V Logic Supplies for the

Control and Serial Ports

Description

The CS4384 is a complete 8-channel digital-to-analog

system. This D/A system includes digital de-emphasis,

half-dB step size volume control, ATAPI channel mix-

ing, selectable fast and slow digital interpolation filters

followed by an oversampled, multi-bit delta sigma mod-

ulator which includes mismatch shaping technology that

eliminates distortion due to capacitor mismatch. Follow-

ing this stage is a multi-element switched capacitor

stage and low-pass filter with single-ended analog

outputs.

The CS4384 also has a proprietary DSD processor

which allows for volume control and 50 kHz on-chip fil-

tering without an intermediate decimation stage. It also

offers an optional path for direct DSD conversion by di-

rectly using the multi-element switched capacitor array.

The CS4384 accepts PCM data at sample rates from

4 kHz to 216 kHz, DSD audio data, and delivers excel-

lent sound quality. These features are ideal for multi-

channel audio systems including SACD players, A/V re-

ceivers, digital TV’s, mixing consoles, effects

processors, and sound cards.

This product is available in 48-pin LQFP package in

Commercial (-40°C to +85°C) temperature grade. See

“Ordering Information” on page 51

for complete details.

C ontrol Port Supply = 1.8 V to 5 V

Register/Hardware

C onfiguration

Internal Voltage

Reference

Reset

S

e

ri

a

l In

te

rf

a

c

e

L

e

v

e

l T

ran

s

lat

o

r

L

e

ve

l T

ra

n

sl

a

tor

TDM Serial

A udio Input

Digital Supply = 2.5 V

Hardw are Mode or

I

2

C /SPI Softw are Mode

C ontrol Data

A nalog Supply = 5 V

E ight C hannels

of Single-E nded

O utputs

8

PC M Serial

A udio Input

Volume

C ontrols

Digital

F ilters

Switch-C ap

DAC and

Analog F ilters

Multi-bit

∆Σ

Modulators

DSD A udio

Input

DSD Processor

-Volume control

-50 kHz filter

E xternal Mute

C ontrol

Mute Signals

2

8

Serial A udio Port

Supply = 1.8 V to 5 V

CS4384

MAY '08

DS620F1

Document Outline

- 1. Pin Description

- 2. Characteristics and Specifications

- Recommended Operating Conditions

- Absolute Maximum Ratings

- DAC Analog Characteristics

- Power and Thermal Characteristics

- Combined Interpolation & On-Chip Analog Filter Response

- Combined Interpolation & On-Chip Analog Filter Response

- DSD Combined Digital & On-Chip Analog Filter Response

- Digital Characteristics

- Switching Characteristics - PCM

- Switching Characteristics - DSD

- Switching Characteristics - Control Port - I·C Format

- Switching Characteristics - Control Port - SPI Format

- 3. Typical Connection Diagram

- 4. Applications

- 4.1 Master Clock

- 4.2 Mode Select

- 4.3 Digital Interface Formats

- Figure 9. Format 0 - Left-Justified up to 24-bit Data

- Figure 10. Format 1 - I·S up to 24-bit Data

- Figure 11. Format 2 - Right-Justified 16-bit Data

- Figure 12. Format 3 - Right-Justified 24-bit Data

- Figure 13. Format 4 - Right-Justified 20-bit Data

- Figure 14. Format 5 - Right-Justified 18-bit Data

- 4.3.1 OLM #1

- 4.3.2 OLM #2

- 4.3.3 OLM #3

- 4.3.4 OLM #4

- 4.3.5 TDM

- 4.4 Oversampling Modes

- 4.5 Interpolation Filter

- 4.6 De-Emphasis

- 4.7 ATAPI Specification

- 4.8 Direct Stream Digital (DSD) Mode

- 4.9 Grounding and Power Supply Arrangements

- 4.10 Analog Output and Filtering

- 4.11 The MUTEC Outputs

- 4.12 Recommended Power-Up Sequence

- 4.13 Recommended Procedure for Switching Operational Modes

- 4.14 Control Port Interface

- 4.15 Memory Address Pointer (MAP)

- 5. Register Quick Reference

- 6. Register Description

- 6.1 Chip Revision (Address 01h)

- 6.2 Mode Control 1 (Address 02h)

- 6.3 PCM Control (Address 03h)

- 6.4 DSD Control (Address 04h)

- 6.5 Filter Control (Address 05h)

- 6.6 Invert Control (Address 06h)

- 6.7 Group Control (Address 07h)

- 6.8 Ramp and Mute (Address 08h)

- 6.9 Mute Control (Address 09h)

- 6.10 Mixing Control (Address 0Ah, 0Dh, 10h, 13h)

- 6.11 Volume Control (Address 0Bh, 0Ch, 0Eh, 0Fh, 11h, 12h, 14h, 15h)

- 6.12 PCM Clock Mode (Address 16h)

- 7. Filter Response Plots

- Figure 28. Single-Speed (fast) Stopband Rejection

- Figure 29. Single-Speed (fast) Transition Band

- Figure 30. Single-Speed (fast) Transition Band (detail)

- Figure 31. Single-Speed (fast) Passband Ripple

- Figure 32. Single-Speed (slow) Stopband Rejection

- Figure 33. Single-Speed (slow) Transition Band

- Figure 34. Single-Speed (slow) Transition Band (detail)

- Figure 35. Single-Speed (slow) Passband Ripple

- Figure 36. Double-Speed (fast) Stopband Rejection

- Figure 37. Double-Speed (fast) Transition Band

- Figure 38. Double-Speed (fast) Transition Band (detail)

- Figure 39. Double-Speed (fast) Passband Ripple

- Figure 40. Double-Speed (slow) Stopband Rejection

- Figure 41. Double-Speed (slow) Transition Band

- Figure 42. Double-Speed (slow) Transition Band (detail)

- Figure 43. Double-Speed (slow) Passband Ripple

- Figure 44. Quad-Speed (fast) Stopband Rejection

- Figure 45. Quad-Speed (fast) Transition Band

- Figure 46. Quad-Speed (fast) Transition Band (detail)

- Figure 47. Quad-Speed (fast) Passband Ripple

- Figure 48. Quad-Speed (slow) Stopband Rejection

- Figure 49. Quad-Speed (slow) Transition Band

- Figure 50. Quad-Speed (slow) Transition Band (detail)

- Figure 51. Quad-Speed (slow) Passband Ripple

- 8. References

- 9. Parameter Definitions

- 10. Package Dimensions

- 11. Ordering Information

- 12. Revision History