Tables 2, Cs4362a – Cirrus Logic CS4362A User Manual

Page 22

22

DS617F2

CS4362A

M1

(DIF1)

M0

(DIF0)

DESCRIPTION

FORMAT

FIGURE

0

0

Left-justified, up to 24-bit data

0

0

1

I²S, up to 24-bit data

1

1

0

Right-justified, 16-bit Data

2

1

1

Right-justified, 24-bit Data

3

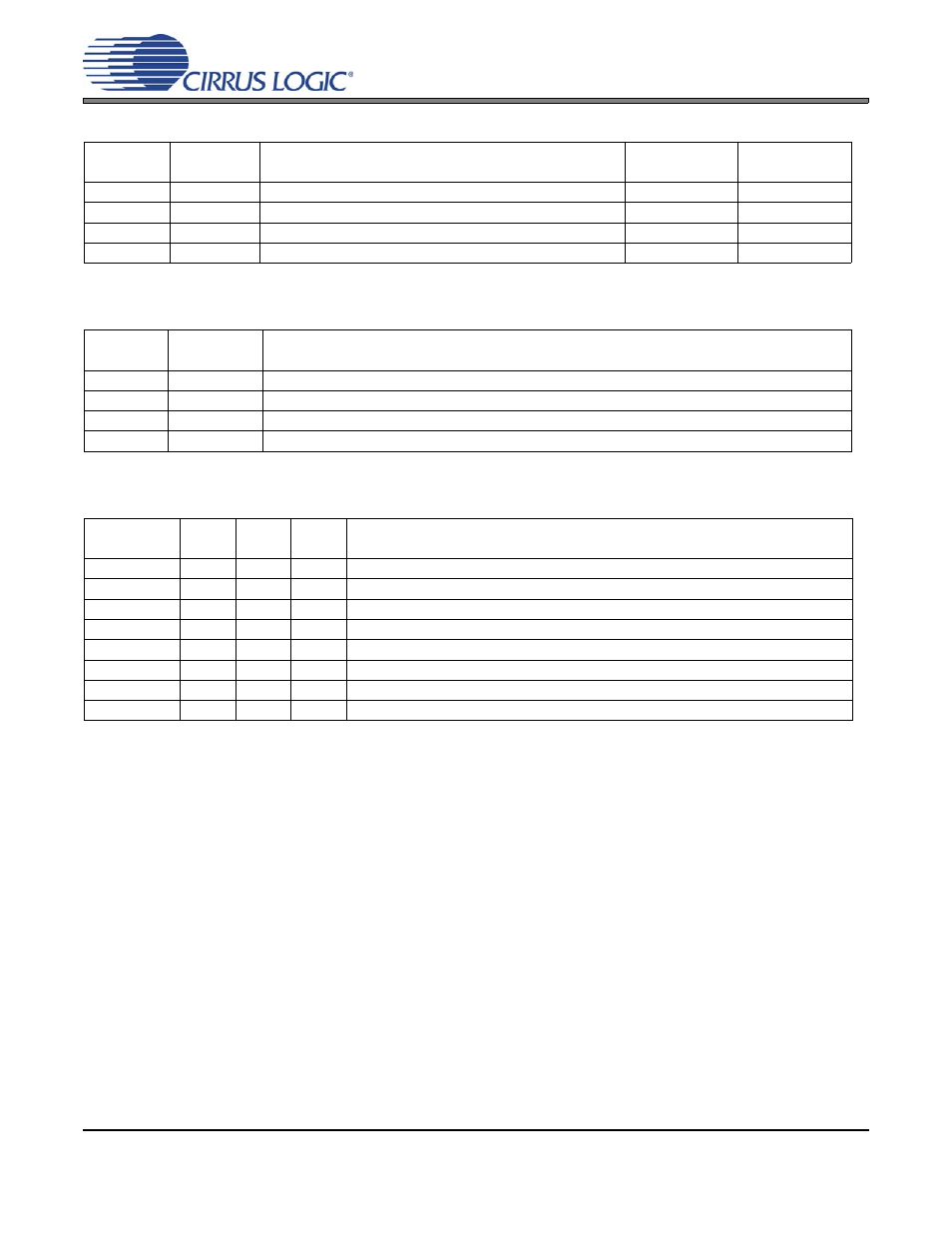

Table 2. Digital Interface Format, Stand-Alone Mode Options

M3

M2

(DEM)

DESCRIPTION

0

0

Single-speed without De-emphasis (4 to 50 kHz sample rates)

0

1

Single-speed with 44.1 kHz De-Emphasis; see

1

0

Double-speed (50 to 100 kHz sample rates)

1

1

Quad-speed (100 to 200 kHz sample rates)

Table 3. Mode Selection, Stand-Alone Mode Options

DSD_EN

(LRCK)

M2

M1

M0

DESCRIPTION

1

0

0

0

64x oversampled DSD data with a 4x MCLK to DSD data rate

1

0

0

1

64x oversampled DSD data with a 6x MCLK to DSD data rate

1

0

1

0

64x oversampled DSD data with a 8x MCLK to DSD data rate

1

0

1

1

64x oversampled DSD data with a 12x MCLK to DSD data rate

1

1

0

0

128x oversampled DSD data with a 2x MCLK to DSD data rate

1

1

0

1

128x oversampled DSD data with a 3x MCLK to DSD data rate

1

1

1

0

128x oversampled DSD data with a 4x MCLK to DSD data rate

1

1

1

1

128x oversampled DSD data with a 6x MCLK to DSD data rate

Table 4. Direct Stream Digital (DSD), Stand-Alone Mode Options