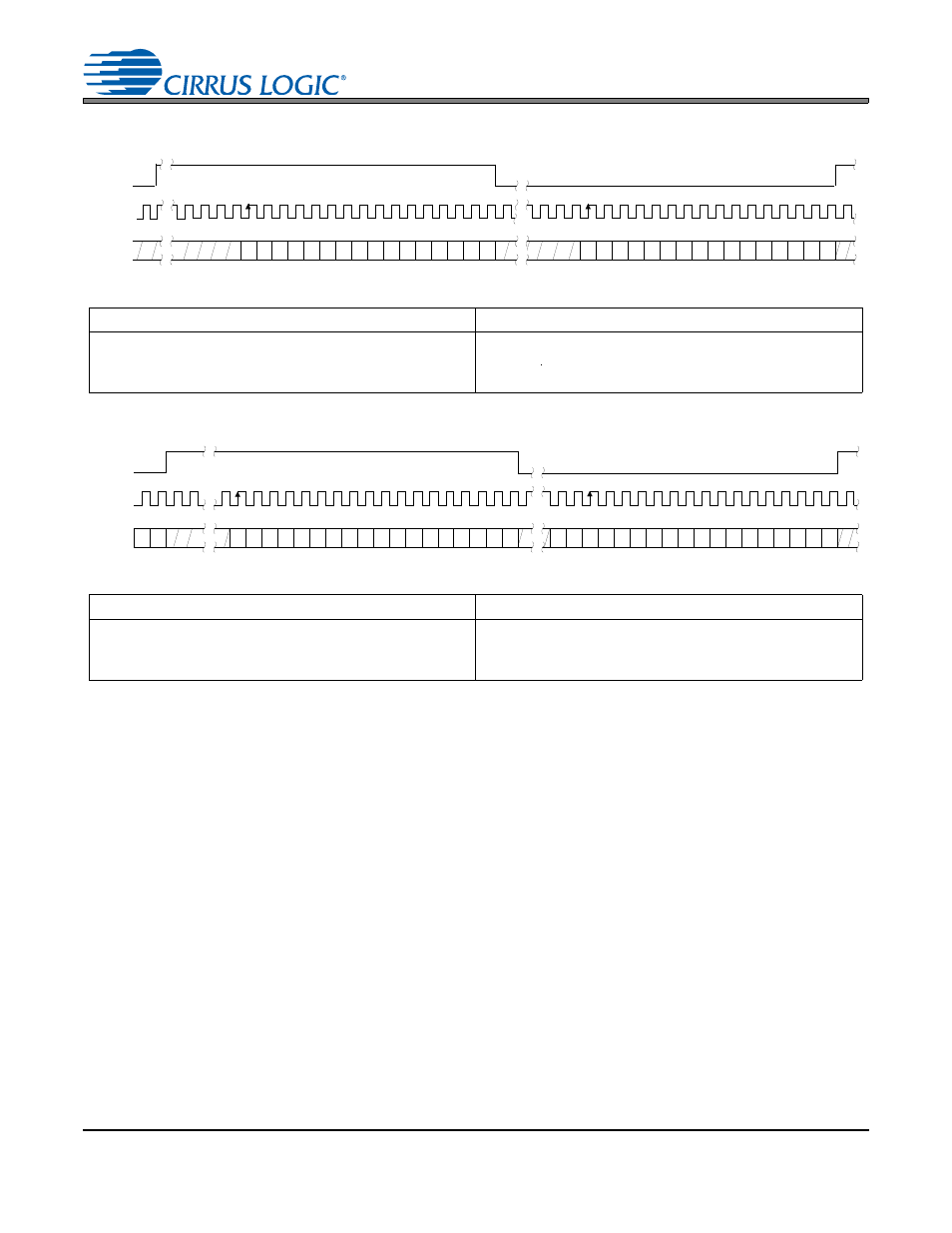

Figure 12. cs4338 data format, Figure 13. cs4339 data format – Cirrus Logic CS4339 User Manual

Page 16

16

CS4334/5/8/9

LRCK

SCLK

Left Channel

Right Channel

SDATA

6

5

4

3

2

1

0

9

8

7

15 14 13 12 11 10

6

5

4

3

2

1

0

9

8

7

15 14 13 12 11 10

32 clocks

Internal SCLK Mode

External SCLK Mode

Right Justified, 16-Bit Data

INT SCLK = 32 Fs if MCLK/LRCK = 512, 256 or 128

INT SCLK = 48 Fs if MCLK/LRCK = 384 or 192

Right Justified, 16-Bit Data

Data Valid on Rising Edge of SCLK

SCLK Must Have at Least 32 Cycles per LRCK Period

Figure 12. CS4338 Data Format

LRCK

SCLK

Left Channel

Right Channel

SDATA

6

5

4

3

2

1

0

9

8

7

15 14 13 12 11 10

1

0

6

5

4

3

2

1

0

9

8

7

15 14 13 12 11 10

17 16

17 16

32 clocks

Internal SCLK Mode

External SCLK Mode

Right Justified, 18-Bit Data

INT SCLK = 64 Fs if MCLK/LRCK = 512, 256 or 128

INT SCLK = 48 Fs if MCLK/LRCK = 384 or 192

Right Justified, 18-Bit Data

Data Valid on Rising Edge of SCLK

SCLK Must Have at Least 36 Cycles per LRCK Period

Figure 13. CS4339 Data Format