Digitalcharacteristics, Digital characteristics, Figure 2. digital input rise and fall times – Cirrus Logic CS3301A User Manual

Page 7: Cs3301a

CS3301A

DS757F1

7

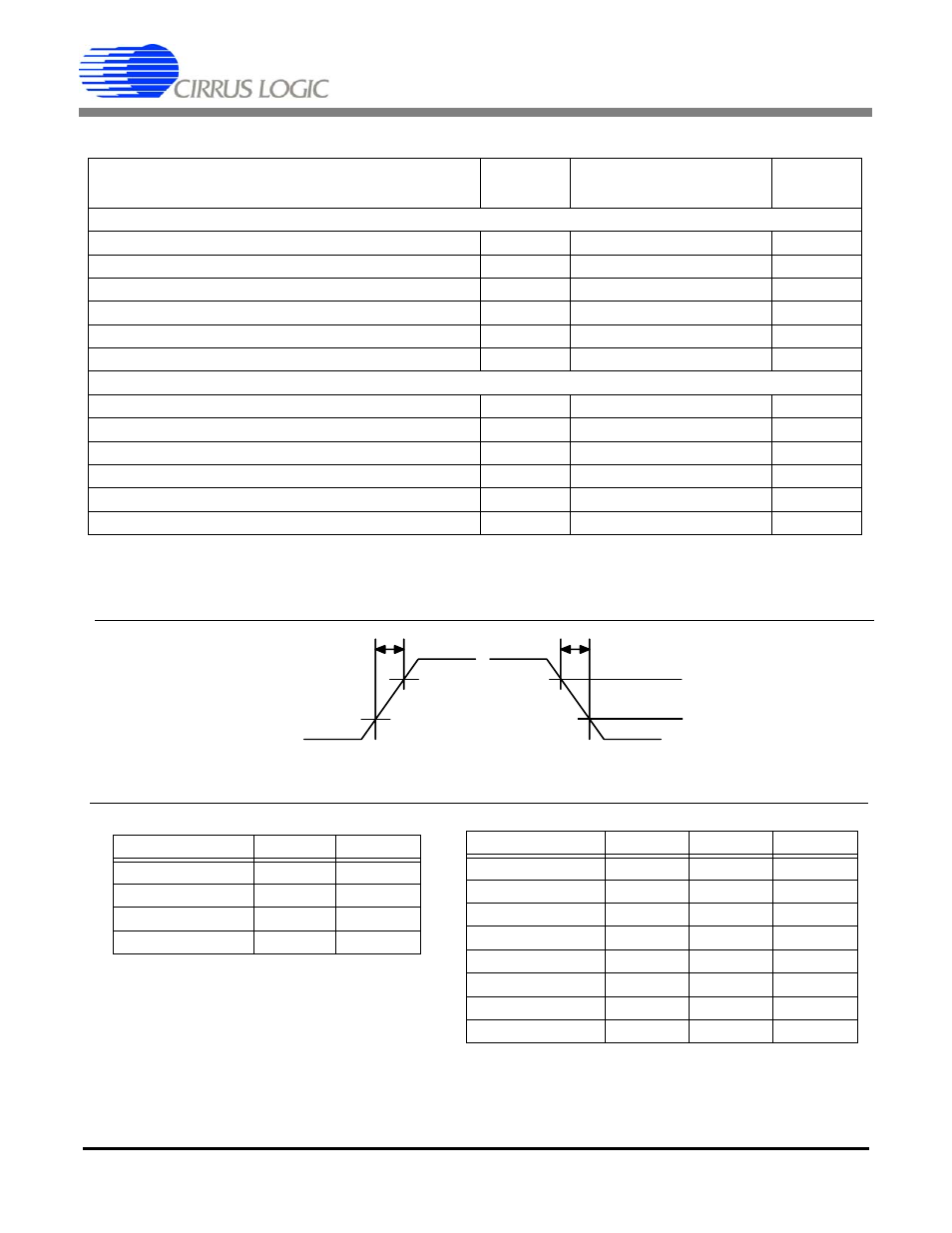

DIGITAL CHARACTERISTICS

Notes: 15. Device is intended to be driven with CMOS logic levels.

16. When CLK is tied to GND, an internal oscillator provides a master clock at approximately 2 MHz. CLK

should be driven for synchronous system operation.

Parameter

Symbol

CS3301A

Unit

Min

Typ

Max

Digital Characteristics

High Level Input Drive Voltage

(

)

V

IH

0.6*VD

-

VD

V

Low Level Input Drive Voltage

(

)

V

IL

0.0

-

0.8

V

Input Leakage Current

I

IN

-

±1

±10

µA

Digital Input Capacitance

C

IN

-

9

-

pF

Rise Times, Digital Inputs Except CLK

t

RISE

-

-

100

ns

Fall Times, Digital Inputs Except CLK

t

FALL

-

-

100

ns

Master Clock Specifications

Master Clock Frequency

(

)

f

CLK

2.0

2.048

2.2

MHz

Master Clock Duty Cycle

f

DTY

40

-

60

%

Master Clock Rise Time

t

RISE

-

-

25

ns

Master Clock Fall Time

t

FALL

-

-

25

ns

Master Clock Jitter (In-Band or Aliased In-Band)

JTR

IB

-

-

300

ps

Master Clock Jitter (Out-of-Band)

JTR

OB

-

-

1

ns

0 .9 * V D

0 .1 * V D

t fa ll

t rise

Figure 2. Digital Input Rise and Fall Times

Gain Selection

GAIN2

GAIN1

GAIN0

x1

0

0

0

x2

0

0

1

x4

0

1

0

x8

0

1

1

x16

1

0

0

x32

1

0

1

x64

1

1

0

reserved

1

1

1

Input Selection

MUX1

MUX0

800

Ω termination

0

0

INA only

1

0

INB only

0

1

INA + INB

1

1

Table 1. Digital Selections for Gain and Input Mux Control