3 memory address pointer, 1 map auto increment, Register quick reference – Cirrus Logic CS2300-CP User Manual

Page 23: Cs2300-cp

CS2300-CP

DS843F2

23

6.3

Memory Address Pointer

The Memory Address Pointer (MAP) byte comes after the address byte and selects the register to be read

or written. Refer to the pseudocode above for implementation details.

6.3.1

Map Auto Increment

The device has MAP auto increment capability enabled by the INCR bit (the MSB) of the MAP. If INCR is

set to 0, MAP will stay constant for successive I²C writes or reads and SPI writes. If INCR is set to 1, MAP

will auto increment after each byte is read or written, allowing block reads or writes of successive regis-

ters.

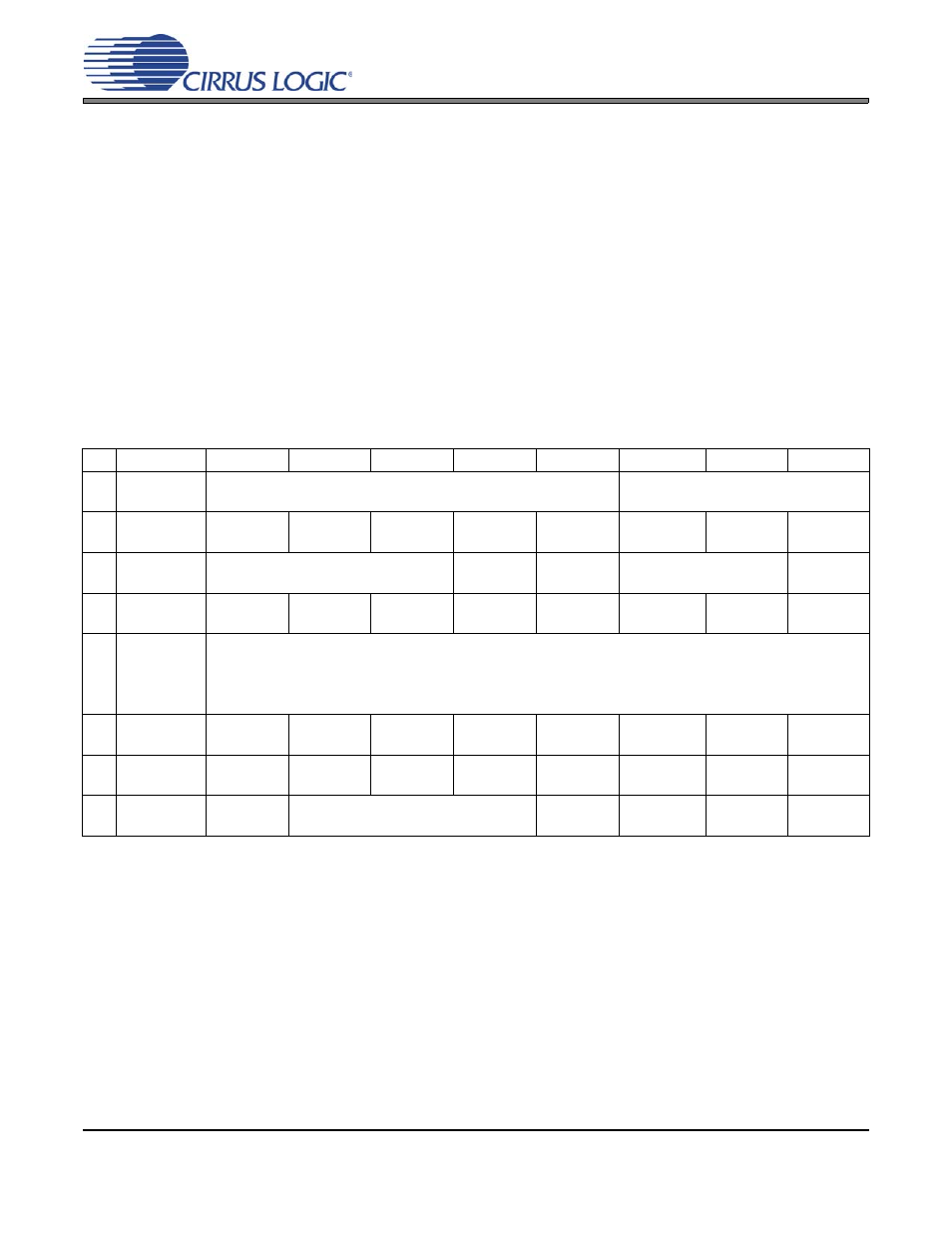

7. REGISTER QUICK REFERENCE

This table shows the register and bit names with their associated default values.

EnDevCfg1, EnDevCfg2, and EnDevCfg3 bits must be set to 1 for normal operation.

WARNING: All “Reserved” registers must maintain their default state to ensure proper functional operation.

Adr Name

7

6

5

4

3

2

1

0

01h

Device ID

Device4

Device3

Device2

Device1

Device0

Revision2

Revision1

Revision0

0

0

0

0

0

x

x

x

02h

Device Ctrl

Unlock

Reserved

Reserved

Reserved

Reserved

Reserved

AuxOutDis

ClkOutDis

x

x

x

0

0

0

0

0

03h

Device Cfg 1

RModSel2

RModSel1

RModSel0

Reserved

Reserved

AuxOutSrc1 AuxOutSrc0 EnDevCfg1

0

0

0

0

0

0

0

0

05h

Global Cfg

Reserved

Reserved

Reserved

Reserved

Freeze

Reserved

Reserved

EnDevCfg2

0

0

0

0

0

0

0

0

06h

-

09h

32-Bit Ratio

MSB

...........................................................................................................................

MSB-7

MSB-8

...........................................................................................................................

MSB-15

LSB+15

...........................................................................................................................

LSB+8

LSB+7

...........................................................................................................................

LSB

16h

Funct Cfg 1

ClkSkipEn AuxLockCfg

Reserved

EnDevCfg3

Reserved

Reserved

Reserved

Reserved

0

0

0

0

0

0

0

0

17h

Funct Cfg 2

Reserved

Reserved

Reserved

ClkOutUnl

LFRatioCfg

Reserved

Reserved

Reserved

0

0

0

0

0

0

0

0

1Eh

Funct Cfg 3

Reserved

ClkIn_BW2 ClkIn_BW1 ClkIn_BW0

Reserved

Reserved

Reserved

Reserved

0

0

0

0

0

0

0

0