9 function configuration 3 (address 1eh), 1 clock input bandwidth (clkin_bw[2:0]), Cs2000-cp – Cirrus Logic CS2000-CP User Manual

Page 33

CS2000-CP

DS761F2

33

8.9

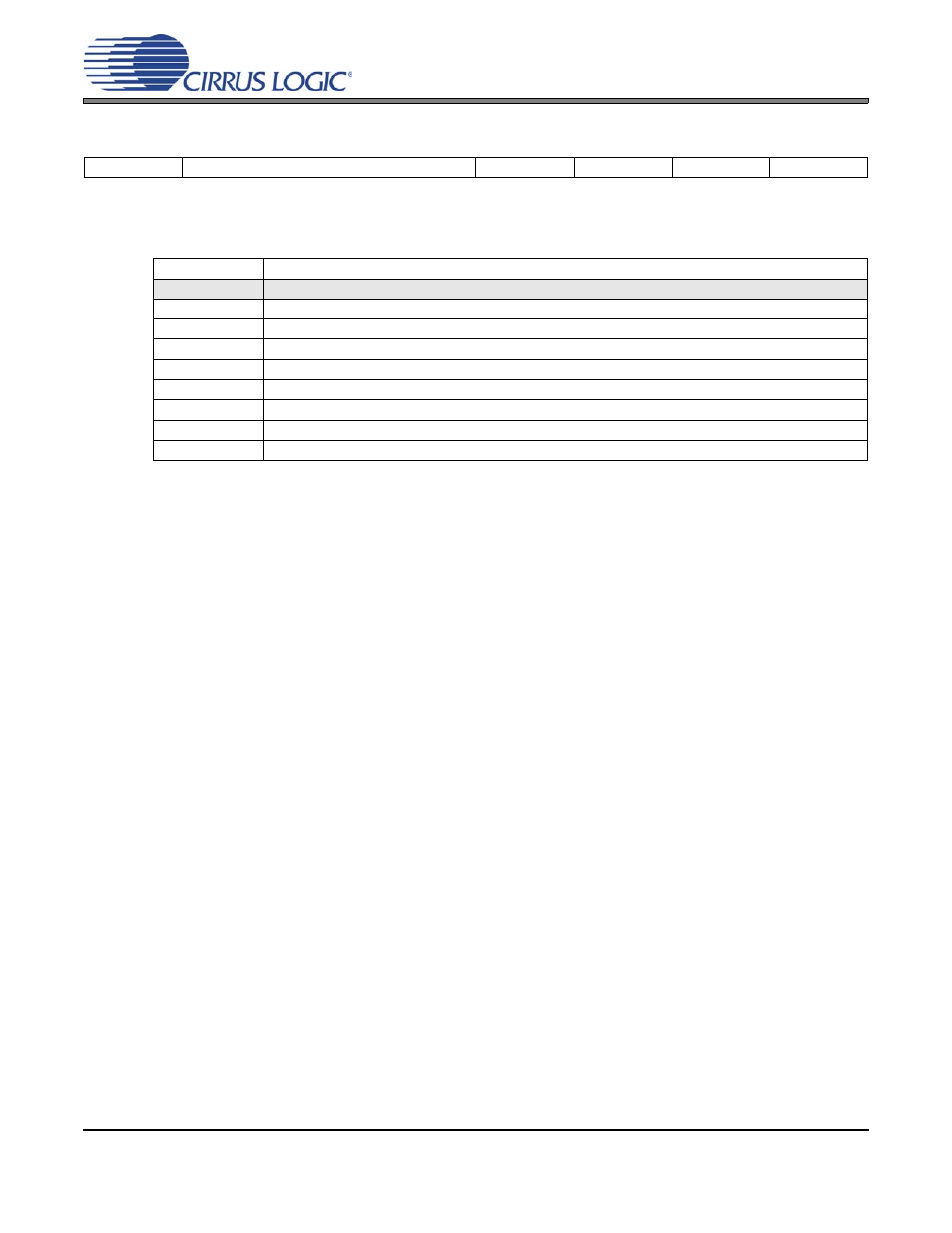

Function Configuration 3 (Address 1Eh)

8.9.1

Clock Input Bandwidth (ClkIn_BW[2:0])

Sets the minimum loop bandwidth when locked to CLK_IN.

Note:

In order to guarantee that a change in minimum bandwidth takes effect, these bits must be set

prior to acquiring lock (removing and re-applying CLK_IN can provide the unlock condition necessary to

initiate the setting change). In production systems these bits should be configured with the desired values

prior to setting the EnDevCfg bits; this guarantees that the setting takes effect prior to acquiring lock.

7

6

5

4

3

2

1

0

Reserved

ClkIn_BW2

ClkIn_BW1

ClkIn_BW0

Reserved

Reserved

Reserved

Reserved

ClkIn_BW[2:0]

Minimum Loop Bandwidth

000

1 Hz

001

2 Hz

010

4 Hz

011

8 Hz

100

16 Hz

101

32 Hz

110

64 Hz

111

128 Hz

Application:

“Adjusting the Minimum Loop Bandwidth for CLK_IN” on page 17

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)