4 device configuration 2 (address 04h), 1 lock clock ratio (lockclk[1:0]), 5 global configuration (address 05h) – Cirrus Logic CS2000-CP User Manual

Page 30: 1 device configuration freeze (freeze), P 30, Cs2000-cp, Device configuration freeze (freeze)

CS2000-CP

30

DS761F2

8.3.4

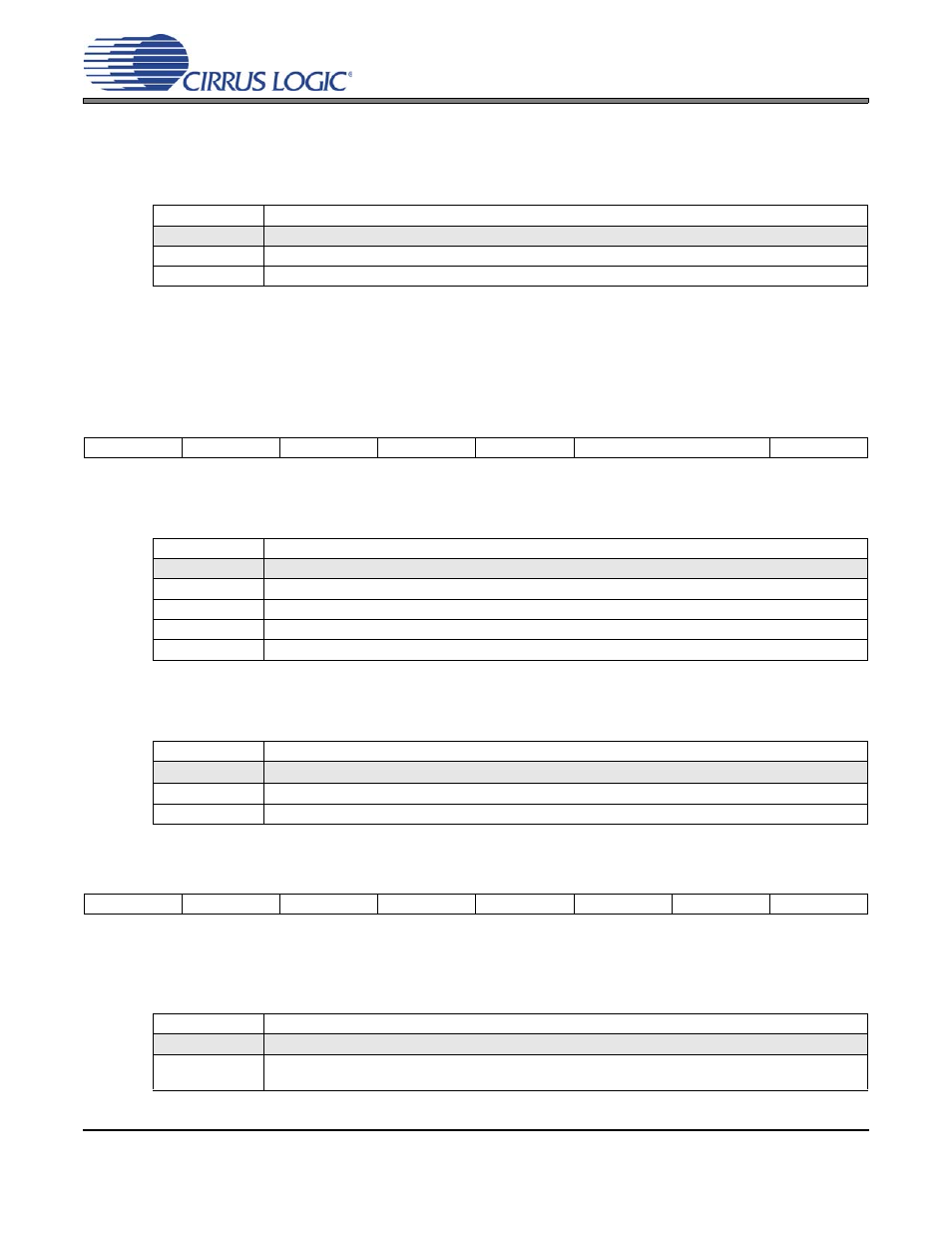

Enable Device Configuration Registers 1 (EnDevCfg1)

This bit, in conjunction with EnDevCfg2, configures the device for control port mode. These EnDevCfg

bits can be set in any order and at any time during the control port access sequence, however they must

both be set before normal operation can occur.

Note:

EnDevCfg2 must also be set to enable control port mode. See

.

8.4

Device Configuration 2 (Address 04h)

8.4.1

Lock Clock Ratio (LockClk[1:0])

Selects one of the four stored User Defined Ratios for use in the dynamic ratio based Hybrid PLL Mode.

8.4.2

Fractional-N Source for Frequency Synthesizer (FracNSrc)

Selects static or dynamic ratio mode when auto clock switching is disabled.

8.5

Global Configuration (Address 05h)

8.5.1

Device Configuration Freeze (Freeze)

Setting this bit allows writes to the Device Control and Device Configuration registers (address 02h - 04h)

but keeps them from taking effect until this bit is cleared.

EnDevCfg1

Register State

0

Disabled.

1

Enabled.

Application:

“SPI / I²C Control Port” on page 24

7

6

5

4

3

2

1

0

Reserved

Reserved

Reserved

Reserved

Reserved

LockClk1

LockClk0

FracNSrc

LockClk[1:0]

CLK_IN Ratio Selection

00

Ratio 0.

01

Ratio 1.

10

Ratio 2.

11

Ratio 3.

Application:

FracNSrc

Fractional-N Source Selection

0

Static Ratio directly from R

EFF

for Frequency Synthesizer Mode

1

Dynamic Ratio from Digital PLL for Hybrid PLL Mode

Application:

“Fractional-N Source Selection” on page 21

7

6

5

4

3

2

1

0

Reserved

Reserved

Reserved

Reserved

Freeze

Reserved

Reserved

EnDevCfg2

FREEZE

Device Control and Configuration Registers

0

Register changes take effect immediately.

1

Modifications may be made to Device Control and Device Configuration registers (registers 02h-04h) without

the changes taking effect until after the FREEZE bit is cleared.