Figure 8, Cs2000-cp – Cirrus Logic CS2000-CP User Manual

Page 13

CS2000-CP

DS761F2

13

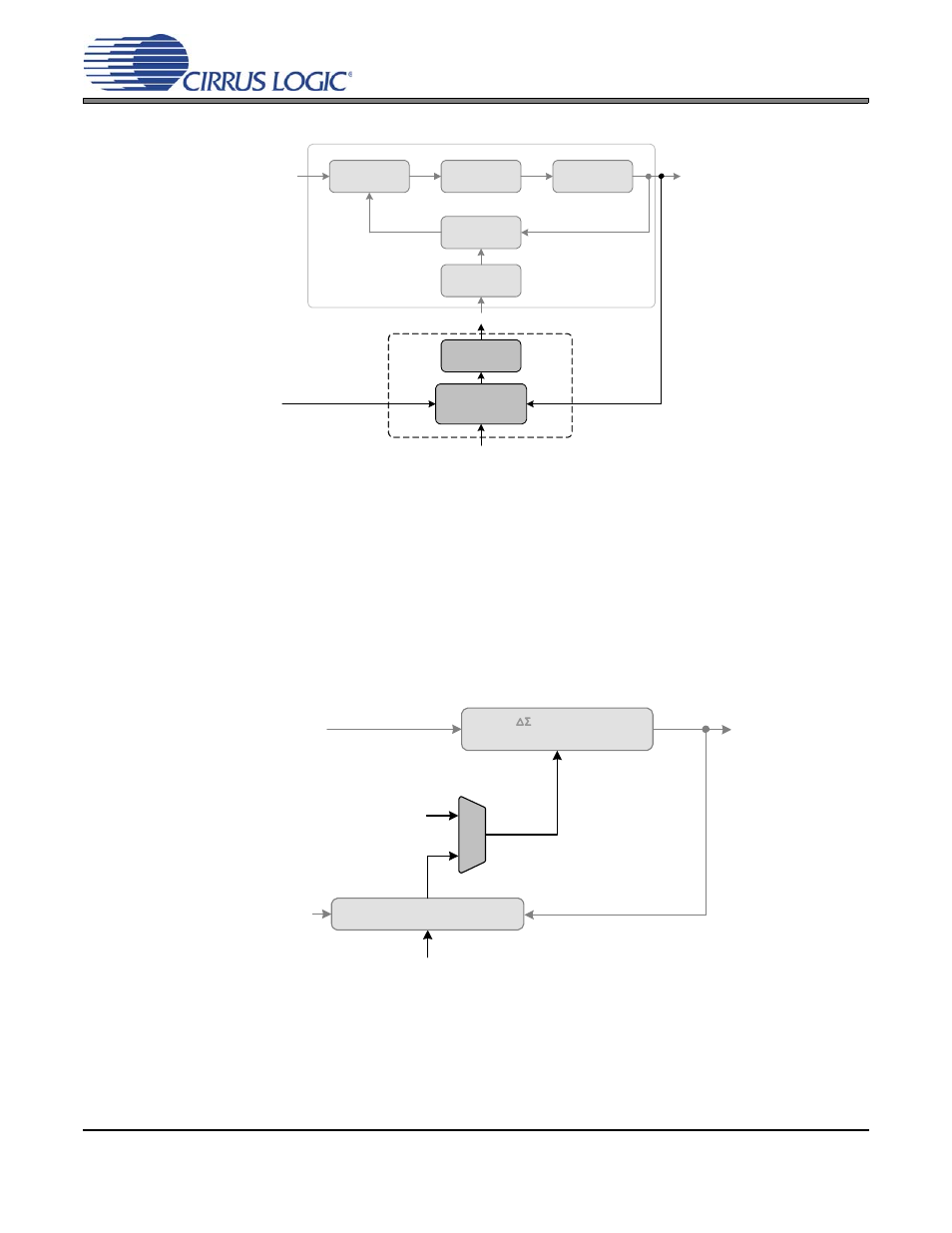

Figure 8. Hybrid Analog-Digital PLL

4.2.1

Fractional-N Source Selection for the Frequency Synthesizer

The fractional-N value for the frequency synthesizer can be sourced from either a static ratio or a dynamic

ratio generated from the digital PLL (see

). This allows for the selection between operating in the

static ratio based Frequency Synthesizer Mode as a simple frequency synthesizer (for frequency gener-

ation from the Timing Reference Clock) and in the dynamic ratio based Hybrid PLL Mode (for jitter reduc-

tion and clock multiplication). Selection between these two modes can either be made automatically

based on the presence of the Frequency Reference Clock or manually through register controls.

.

Figure 9. Fractional-N Source Selection Overview

N

Digital Filter

Frequency

Comparator for

Frac-N Generation

Frequency Reference

Clock

Delta-Sigma Fractional-N Frequency Synthesizer

Digital PLL and Fractional-N Logic

Output to Input Ratio for Hybrid mode

Fractional-N

Divider

Timing Reference

Clock

PLL Output

Voltage Controlled

Oscillator

Internal

Loop Filter

Phase

Comparator

Delta-Sigma

Modulator

Frequency Reference Clock

Output to Input ratio for Hybrid Mode

Timing Reference Clock

PLL Output

Fractional-N

Frequency Synthesizer

Digital PLL & Fractional-N Logic

Output to Input Ratio for Synthesizer Mode

N