An312 – Cirrus Logic AN312 User Manual

Page 8

8

AN312REV2

AN312

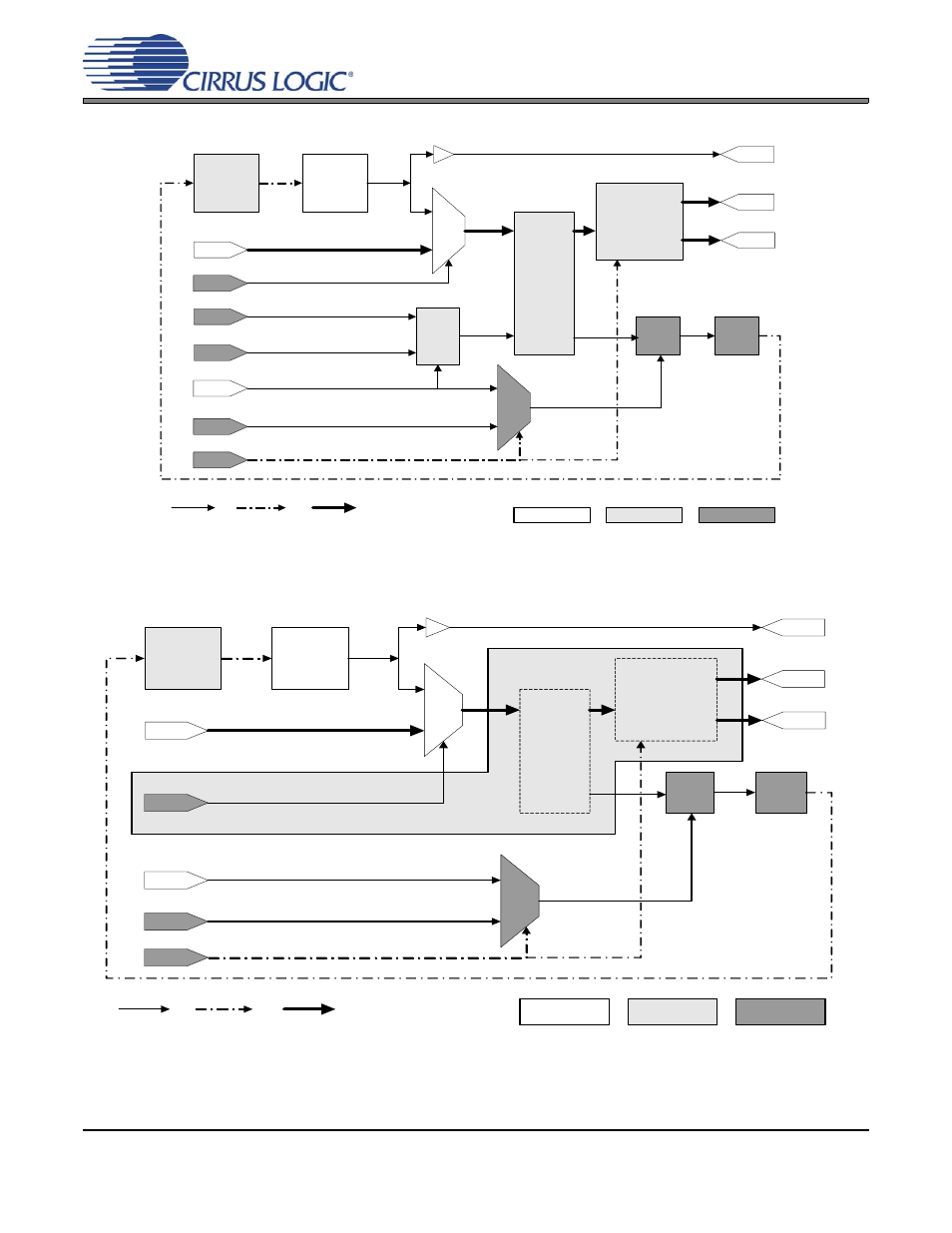

Figure 13. Clock Circuit as Used by Mode 0x04 with CM-1 Module

Figure 14. Clock Circuit as Used by Mode 0x04 with CM-2 and Semiconductors

B eat R eceived

VC X O

24.576M H z

+/- 100 PPM

D AC

M C LK_IN

M C LK_SEL

R EFC LK_Enable

R EFC LK _Polarity

R E FC LK

Edge

D etect

M C LK

M U X

B eat

M U X

Phase

D etector

Sam ple

Phase

C ounter

R ST

Loop

Filter

control

C lock

O ut

M C LK_O U T (m aster)

F S1 (w ord)

SC K (bit)

Audio

C lock

G enerator

C lock C onfig

Signal

Path

C ontrol

Path

H ardw are

FPG A

Softw are

Active

Signal

P ath

B e a t R e c e iv e d

V C X O

2 4 .5 7 6 M H z

+ /- 1 0 0 P P M

D A C

M C L K _ IN

M C L K _ S E L

R E F C L K

M C L K

M U X

B e a t

M U X

P h a s e

D e te c to r

S a m p le

P h a s e

C o u n te r

L o o p

F ilte r

c o n tro l

C lo c k

O u t

M C L K _ O U T (m a s te r)

F S 1 (w o rd )

S C K (b it)

A u d io

C lo c k

G e n e ra to r

C lo c k C o n fig

S ig n a l

P a th

C o n tro l

P a th

E x te rn a l

H a rd w a re

C o b ra N e t

P ro c e s s o r

S o ftw a re

A c tiv e

S ig n a l

P a th