An312 – Cirrus Logic AN312 User Manual

Page 11

AN312REV2

11

AN312

3.1.6

0x14 Mode for CM-2/CS1810xx/CS4961xx-Based Devices

Note:

The 0x14 clock mode only works with devices running Rev. 2.11.6 firmware or later.

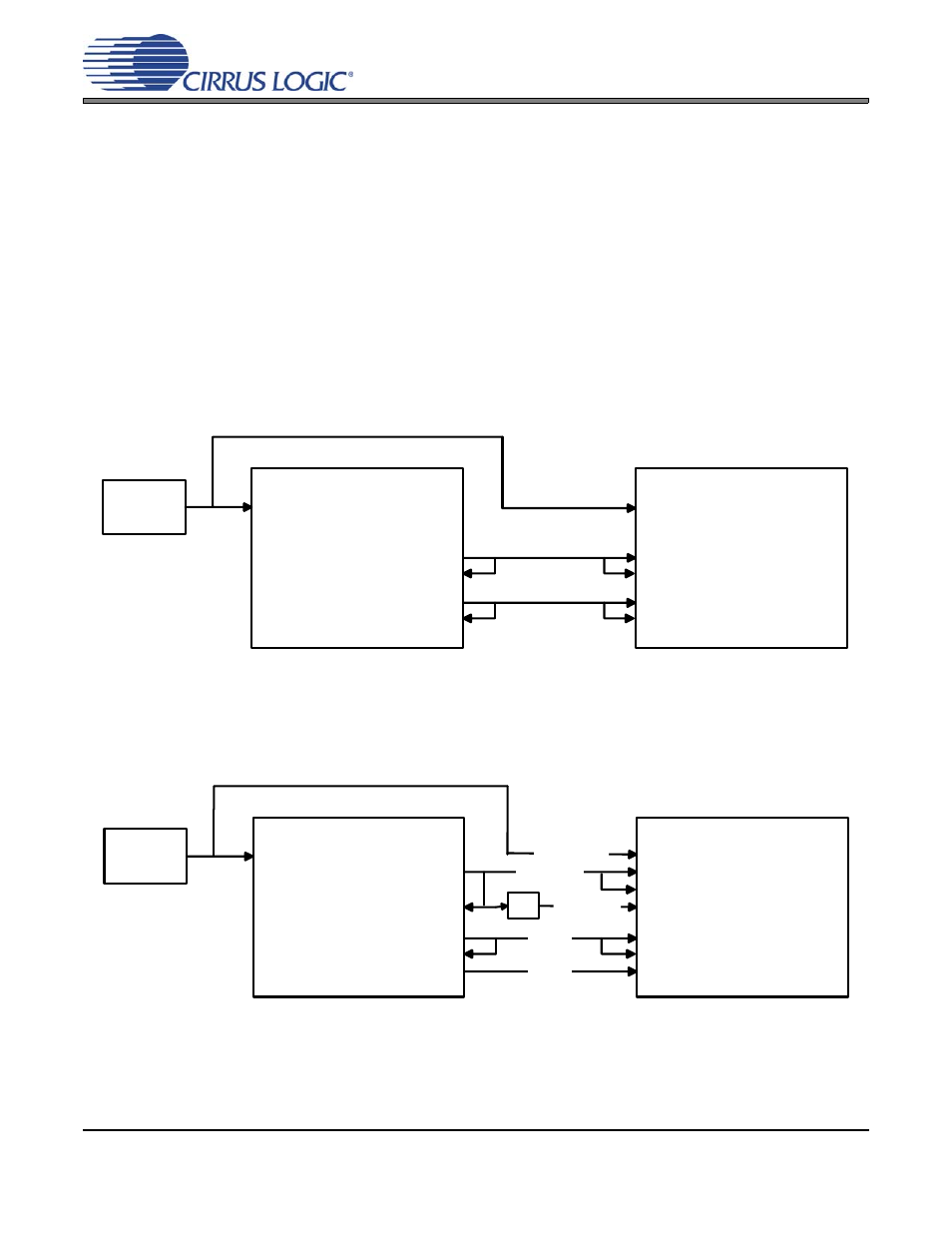

Mode 0x14 for CM-2 and CobraNet chips is primarily intended to allow complete audio clock slaving of

one or more CobraNet devices to a master CobraNet device within the same chassis.

MCLK, SCLK, and FS1 are all supplied to the slave device by the master device. External divide by 2 logic

must also be used on DAI1_SCLK when using 16x16 channel chips.

Changing to this mode dynamically has not proven to work well consistently. The CNCustom firmware

modification program should be used to create slave device firmware with the Conductor and Performer

clock modes set to values of 0x14 so that the slave device(s) will boot up in mode 0x14. The hardware

should be designed so that the slave device(s) will always be supplied by all required clocks and will al-

ways operate in mode 0x14. The internal clock circuitry for the master device will be as that shown and

described elsewhere in this document for the master clock mode in use. A description of the internal clock

circuitry is not applicable for the slave device(s) as all clocks are supplied to them directly.

Figure 18. Clock Circuit as Used by Mode 0x14 with CM-2 or Chips with 2x2 or 8x8 Audio Channels

Figure 19. Clock Circuit as Used by Mode 0x14 with CM-2 or Chips with 16x16 Audio Channels

3.072 / 6.144 MHz

24.576 MHz

MCLK_IN (8)

DAI1_LRCLK (138)

48 / 96 kHz

MCLK_IN (8)

DAI1_SCLK (137)

CobraNet Interface

(Slave)

Mode 0x14

CobraNet Interface

(Master)

(Typically Mode 0)

DAO1_SCLK (20)

DAO1_LRCLK (22)

DAO1_SCLK (20)

VCXO

DAI1_SCLK (137)

DAI1_LRCLK (138)

DAO1_LRCLK (22)

6.144 MHz

24.576 MHz

MCLK_IN (8)

DAI1_LRCLK (138)

96 kHz

MCLK_IN (8)

DAI1_SCLK (137)

CobraNet Interface

(Slave)

Mode 0x14

CobraNet Interface

(Master)

(Typically Mode 0)

DAO1_SCLK (20)

DAO1_LRCLK (22)

DAO1_SCLK (20)

VCXO

DAI1_SCLK (137)

DAI1_LRCLK (138)

DAO1_LRCLK (22)

DAO2_SCLK (12)

/2

3.072 MHz

48 kHz

DAO2_LRCLK (14)

DAO2_LRCLK (14)