Dram clock/drive control, Dram timing [auto by spd, Dram cas latency [2.5 – Asus A7V400-MX User Manual

Page 48: Bank interleave [disabled, Precharge to active (trp) [5t, Active to precharge (tras) [7t, Active to cmd (trcd) [5t, Dram burst lenght [4, 16 chapter 2: bios information, Configuration options: [disabled] [2 bank] [4 bank

2-16

Chapter 2: BIOS information

DRAM Timing [Auto by SPD]

It is recommended that you set this parameter to [Auto by SPD]. Setting to

[Auto by SPD] synchronizes the DRAM timing with the DRAM clock. Setting to

[Manual] allows you to set the values for DRAM CAS Latency, Bank Interleave,

Pre-charge to Active (TRP) and Active to CMD (Trcd) prameters.

Configuration options: [Manual] [Auto By SPD] [Safe]

DRAM CAS Latency [2.5]

This field sets the override clock cycle for the latency time between the DRAM read

command and the moment that the data actually becomes available. Normally, the

system determines the rate automatically by default.

Configuration options: [1.5] [2] [2.5] [3]

Bank Interleave [Disabled]

Configuration options: [Disabled] [2 Bank] [4 Bank]

Precharge to Active (Trp) [5T]

Configuration options: [2T] [3T] [4T] [5T]

Active to Precharge (Tras) [7T]

Configuration options: [6T] [7T] [8T] [9T]

Active to CMD (Trcd) [5T]

Configuration options: [2T] [3T] [4T] [5T]

DRAM Burst Lenght [4]

Configuration options: [4] [8]

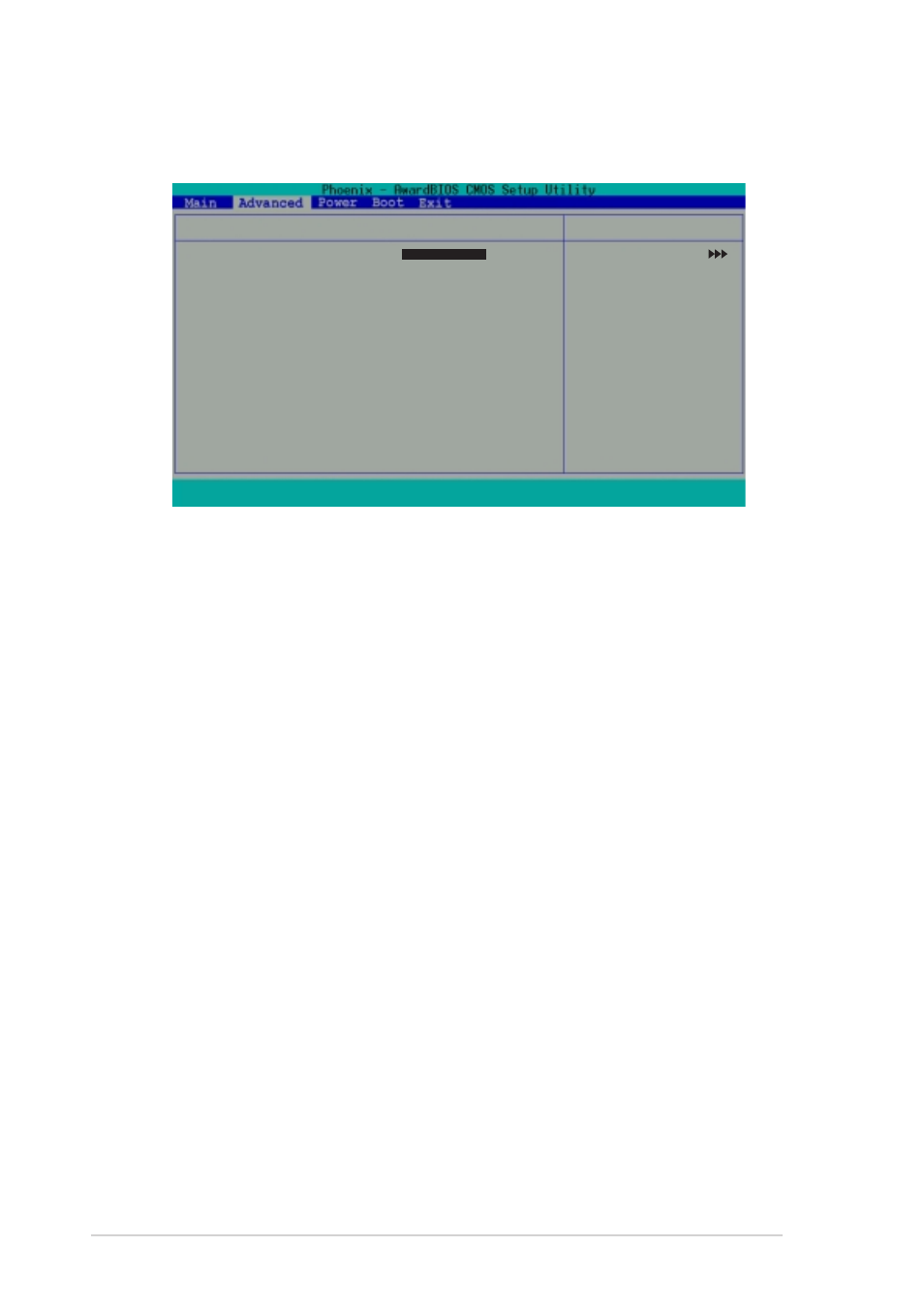

DRAM Clock/Drive Control

DRAM Timing

[Auto by SPD]

DRAM CAS Latency

[2.5]

Bank Interleave

[Disabled]

Pre-charge to Active (Trp)

[5T]

Active to Precharge (Tras)

[7T]

Active to CMD (Trcd)

[5T]

DRAM Burst Length

[4]

DRAM Command Rate

[2T Command]

Write Recovery Time

[3T]

tWTR

[2T]

DRAM Clock/Drive Control

F1

: Help

↑↓

↑↓

↑↓

↑↓

↑↓

: Select Item

-/+

: Change Value

F5

: Setup Defaults

ESC : Exit

→←

→←

→←

→←

→←

: Select Menu

Enter : Select Sub-menu

F10 : Save and Exit

Select Menu

Item Specific Help