Bit rate and find bit rate, Hs (high speed) tests, Brief hs clock to data timing test descriptions – Teledyne LeCroy MIPI D-PHY User Manual

Page 8: Brief hs data timing test descriptions

MIPI D-PHY

8

918800 RevA

Bit Rate and Find Bit Rate

These fields allow you to either enter a specific Bit Rate, or have MIPI D-PHY find your signal's bitrate.

HS (High Speed) Tests

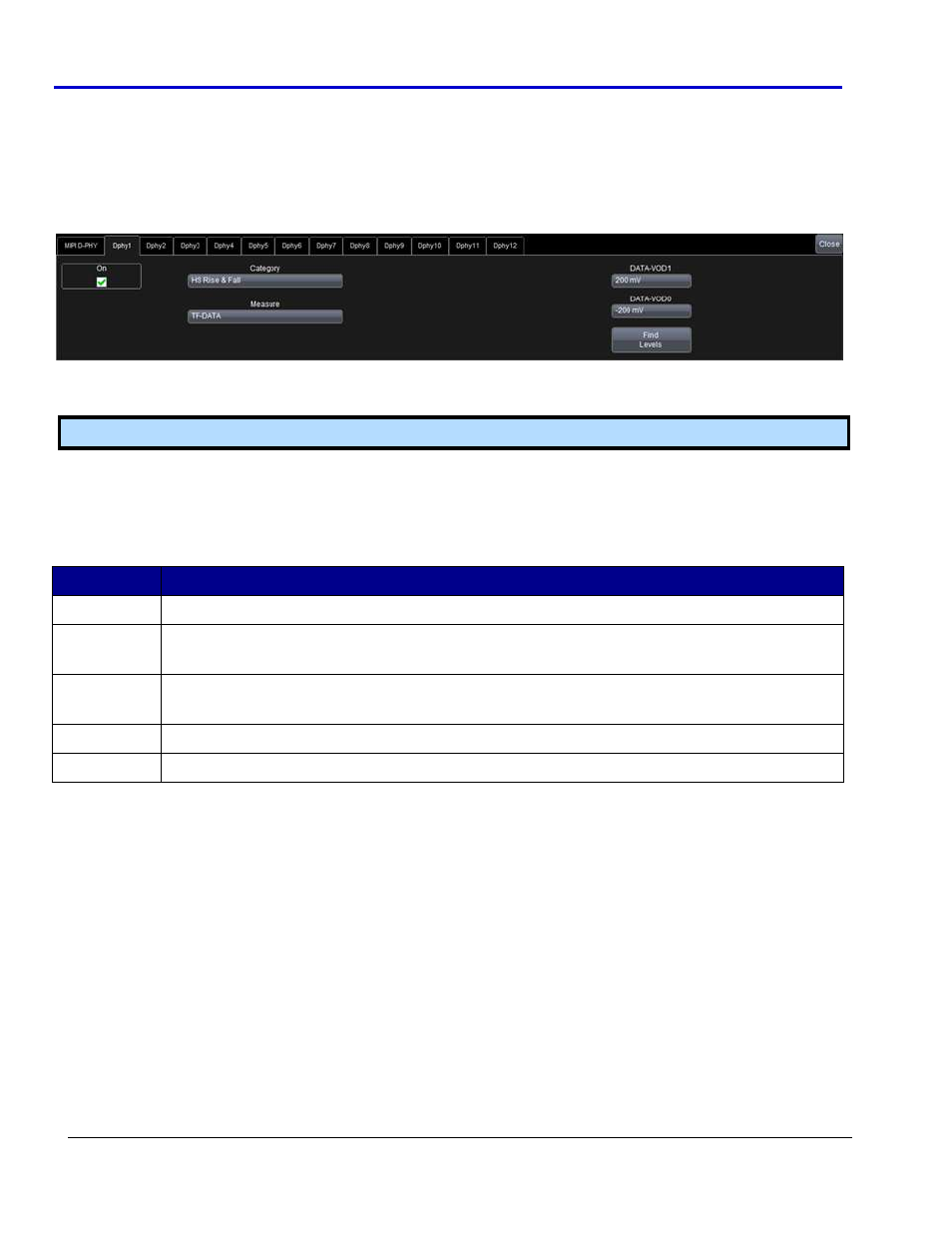

All Dphy1 - 12 dialogs have On, Category, and Measure controls. When the HS Rise & Fall category is selected,

DATA/CLK-VOD1, DATA/CLK-VOD0, and Find Levels controls are also shown.

With HS (High Speed) selected as your Mode on the Mode and Input Selection Area of the MIPI D-PHY Dialog

(on page 6), Categories and Measurements on the Dphy1 - 12 dialogs vary in the following manner.

Note: For LP (Low Power) Tests, refer to the LP (Low Power) Tests (on page 11) topic.

Category and Measure Combinations for HS Dphy1 - 12 Dialogs

With HS Clock To Data Timing selected in the Category field, the following Measure values are available:

FirstBit, TCLK-PRE, TCLK-POST, TSETUP, and THOLD.

BRIEF HS CLOCK TO DATA TIMING TEST DESCRIPTIONS

Name

Purpose

FirstBit

To verify that the DUT HS Clock is properly aligned to the payload data signaling.

TCLK-PRE

To verify that the time that the HS clock is driven prior to an associated Data Lane beginning the

transition from LP to HS mode (TCLK-PRE), is greater than the minimum required value.

TCLK-POST

To verify that the DUT Clock Lane HS transmitter continues to transmit clock signaling for the

minimum required duration (TCLK-POST) after the last Data Lane switches to LP mode.

TSETUP

To verify the Setup time between the clock and data signaling is within conformance limits.

THOLD

To verify the Hold time between the clock and data signaling is within conformance limits.

With HS Data Timing selected in the Category field, the following Measure values are available:

TLP-01, THS-PREPARE, THS-ZERO, THS-PREPARE+ZERO, THS-SYNC, THS-TRAIL, TEOT, TREOT, and THS-

EXIT.