Teledyne LeCroy HPT - Users Manual User Manual

Page 13

CATC

HPT User’s Manual

Version 2.27

Page 11

•

If the USB interrupt count doesn’t match the expected count (21), it will be displayed as

WRONG, followed by a number representing the actual USB interrupts encountered.

•

The power state will be displayed as BAD if power wasn’t provided by the host on the

corresponding USB port. If all test sequences failed for a particular USB port, the power state

is displayed as N/A.

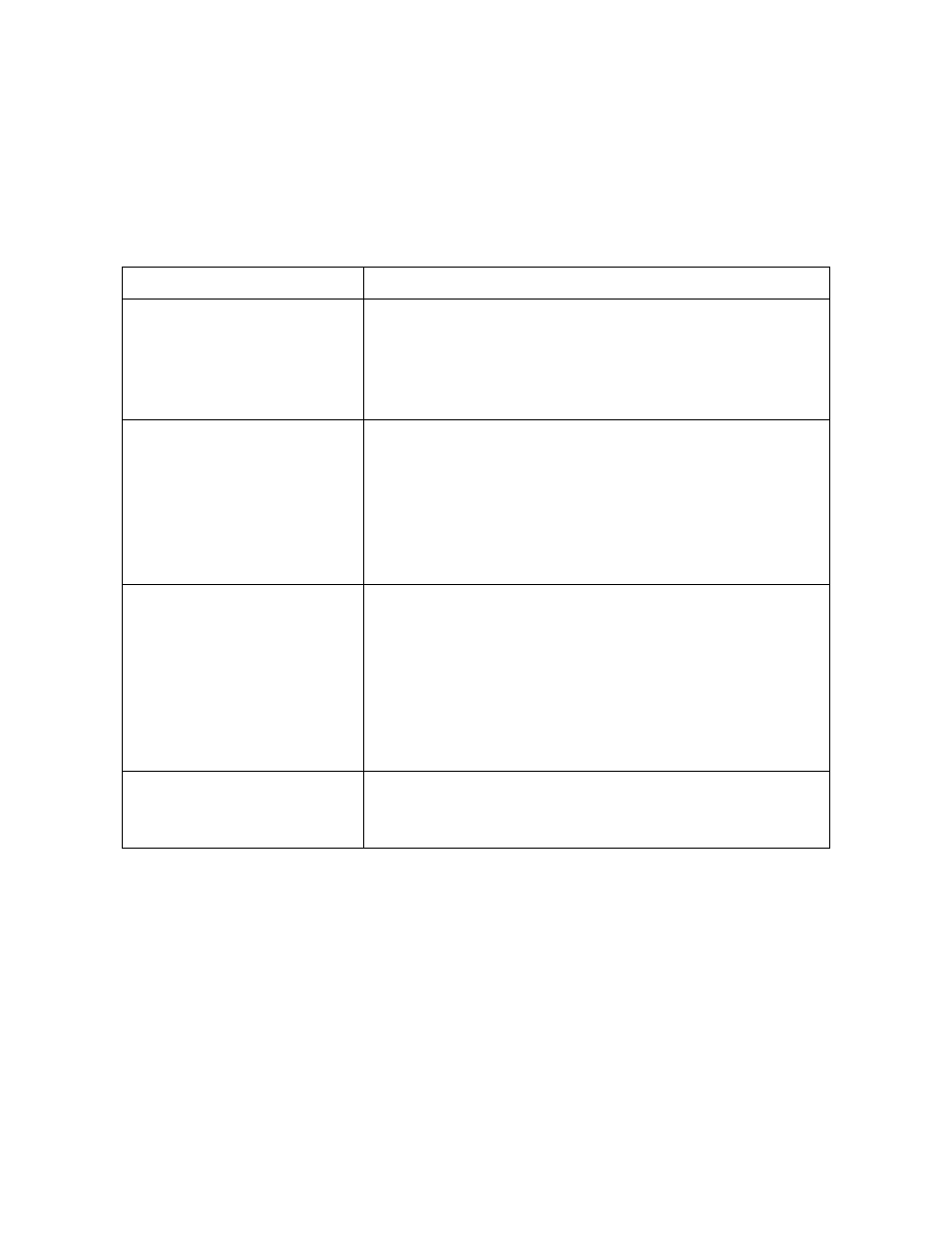

For UHCI systems, the HPR error classes are interpreted as follows:

HPT Error Class:

UHCI Error Type:

USB errors

The Host Controller sets this bit when completion of a

USB transaction results in an error condition (e.g., error

counter underflow). If the Transfer Descriptor on which

the error interrupt occurred also had its IOC bit set, both

this bit and Bit 0 are set.

host system errors

The Host Controller sets this bit when a serious error

occurs during a host system access involving the Host

Controller module. In a PCI system, such errors include

PCI Parity error, PCI Master Abort, and PCI Target Abort.

When this error occurs, the Host Controller clears the

Run/Stop bit in the Command register to prevent further

execution of scheduled Transfer Descriptors.

host controller process errors

The Host Controller sets this bit when it detects a fatal

error; it indicates that the Host Controller suffered a

consistency check failure while processing a Transfer

Descriptor. An example is finding an illegal PID field

while processing the packet header portion of the Transfer

Descriptor. When this error occurs, the Host Controller

clears the Run/Stop bit in the Command register to prevent

further execution of scheduled Transfer Descriptors.

wrong transfer status errors

This bit is set when one of the error bits (i.e., Stalled, Data

Buffer Error, Babble Detected, or CRC/Time Out Error) in

the status field of a transfer is set upon completion.