Trigger modes, Inputs and outputs, Trigger output – Atec Agilent-81100 Series User Manual

Page 10

Data Sheet 81100 Family of Pulse Pattern Generators

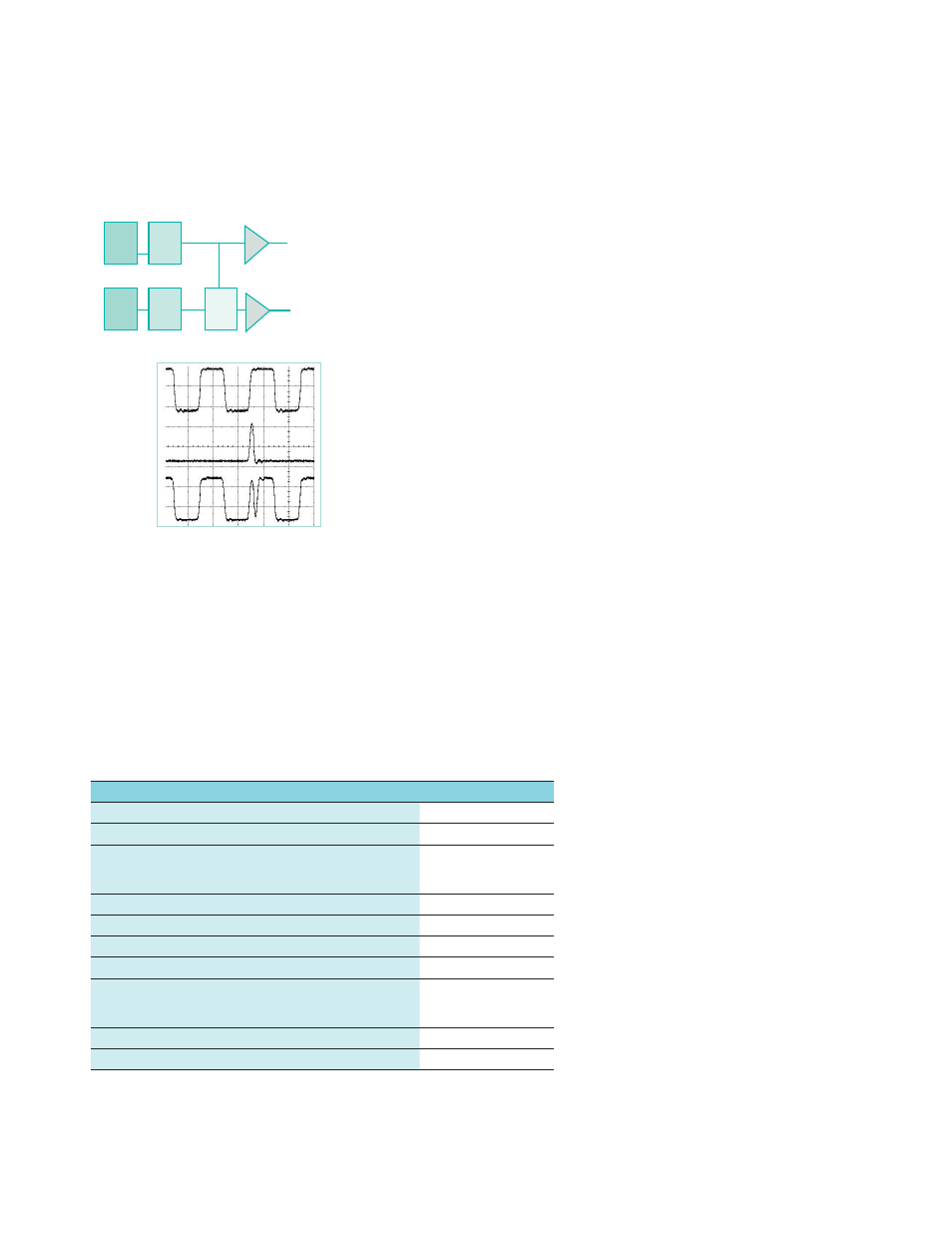

Digital channel addition

Channel 1 can be logically combined with

channel 2 (XOR) as shown in Figure 2. The

source impedance remains 50 Ω. Output 2

is still available in this case.

Trigger modes

Continuous: Continuous pulses, bursts or

patterns.

External started: Each active input transi-

tion (rising, falling edge) generates pulses,

bursts or patterns.

External gated: The active input level

(high or low) enables pulses, bursts or

patterns. On an external gate signal the

output is immediately stopped, that means

the last cycle will not be completed.

Manual: Simulates an external input

signal with push of a front panel button.

Inputs and outputs

Clock input/PLL reference and

external input

Connectors: SMA (f) 3.5 mm

Input impedance: 50 Ω

Termination voltage: -2.10 V to 3.30 V

Input sensitivity: < 400 mV typ.

Max. input voltage: -3 V to + 6 V

Input transitions: < 20 ns

Only valid for clock input/PLL reference

One input is used for clock input or for the

PLL reference alternatively.

Reference: The internal PLL is locked to

the 1,2,5 or 10 MHz. The output frequency

of the instrument must be larger than the

clock input/PLL reference frequency.

External clock: The output period is

determined by the signal at clock input.

Clock input frequency: 170 kHz to 660 MHz

(at 50% ±10% duty cycle).

Delay from input trigger output: 21 ns.

Delay from input to output: 53 ns.

Threshold: ac coupled. Only valid for external

input.

External input: Used for external started or

gated.

Input frequency: DC to 330MHz.

Delay from external input to trigger output:

22ns + 0 to 1 period.

Delay from external input to output:

54 ns + 0 to 1 period.

Threshold: -1.4 V to +3.7 V.

Trigger output

Trigger format: One pulse per period with

50% duty cycle typical. In pattern mode the

trigger pulse can be set to mark the start of

any segment.

Output impedance: 50 Ω typical.

Level: TTL/ETTL (for frequency < 180 MHz),

1 V to GND, ECL 50 Ω to GND/-2 V, PECL

50 Ω to + 3 V.

Max. external voltage: -2 V/+3 V.

Transition times: 1.0 ns typical for TTL,

600 ps typical for ECL.

Delay from external input to trigger output:

32 ns typical.

Channel 1

XOR

Delay,

width

Delay,

width

Data

Data

Channel 2

Channel 1 +

Channel 1

Channel 2

Channel 1

Channel 2

Channel 1 +

Channel 2

Figure 2: Channel addition

10

Programming times: (measured at display off)

ASCII command

Typical execution time

Width, delay, transition times

40 ms to 70 ms

Period within one range 1

100 ms to 260 ms

Period between different ranges:1

• In pulse/burst mode

• in pattern mode

140 ms to 300 ms

100 ms to 5.05 s

Levels

43 ms

Trigger modes

< 75 ms

Input parameters

28 ms

Save setting

200 ms

Recall setting:

a) In pulse/burst mode

b) In pattern mode with data and PRBS (depends on setting)

515 ms to 800 ms

1.15 s to 5.5 s

65504 bit pattern transfer

1.25 s

Pattern and sequencing (depends on setting)

190 ms to 5.1 s

1. Range depends on segment length resolution, see previous table.