Voltage detector az70xx data sheet, Operating diagram (continued) typical applications – Diodes AZ70XX User Manual

Page 9

9

BCD Semiconductor Manufacturing Limited

VOLTAGE DETECTOR AZ70XX

Data Sheet

Oct. 2011 Rev. 2. 2

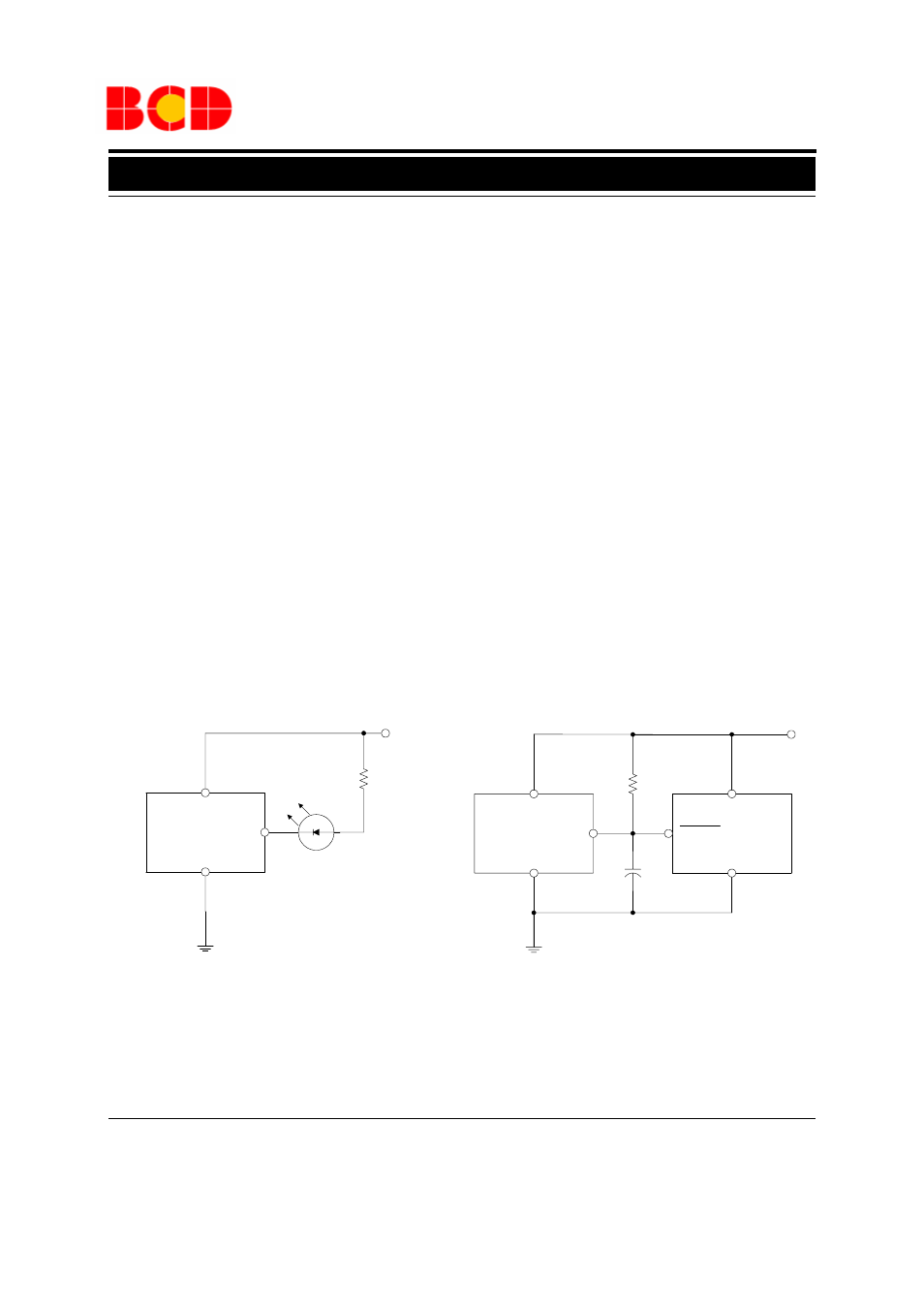

Figure 13. Low Voltage Indicator

Figure 14. CPU Resetting Circuit

1

3

2

V

CC

AZ70XX

OUT

GND

LED

V

CC

R1

220

V

CC

+5V

R1

3.3k

1

3

2

V

CC

AZ70XX

OUT

GND

CPU

V

CC

GND

RESET

C1

1

µF

+

Operating Diagram (Continued)

Typical Applications

Figure 12 is a typical timing waveform for AZ70XX.

In normal steady-state operation when V

CC

>V

DET-

,

the

output will be in a logic high state and V

OUT

is

dependent upon the voltage that the pull-up resistor

connected to.

Here is some explanations for AZ70XX's operation.

1. When the input voltage V

CC

falls below V

DET-

, the

output will pull down to logic low after a delay time of

tpHL. In general, at rated output current and V

CC

,

V

OUT

can be pulled down to a voltage as low as within

0.4V from GND. (See the Electrical Characteristics

section). The voltage level V

DET-

means the detect

voltage.

2. The output, V

OUT

, will stay valid until V

CC

falls

below the minimum operating voltage, V

OPR

(0.8V

typical). Below minimum operating voltage, the out-

put is undefined.

3. During power-up, V

OUT

will remain undefined until

V

CC

rises above V

OPR

, at which time the output will

become valid. V

OUT

will be in its active low state

while V

OPR

CC DET+ (V DET+ =V DET- +V HYS ). V DET+ is the release voltage. V HYS means the hystere- sis voltage and is the difference voltage between the DET+ and V DET- . 4. When V CC rises above V DET+ , the output will be in its inactive state. After a delay time of tpLH, V OUT will be in its logic high state .

V