Functional description – Rainbow Electronics LM81 User Manual

Page 28

Functional Description

(Continued)

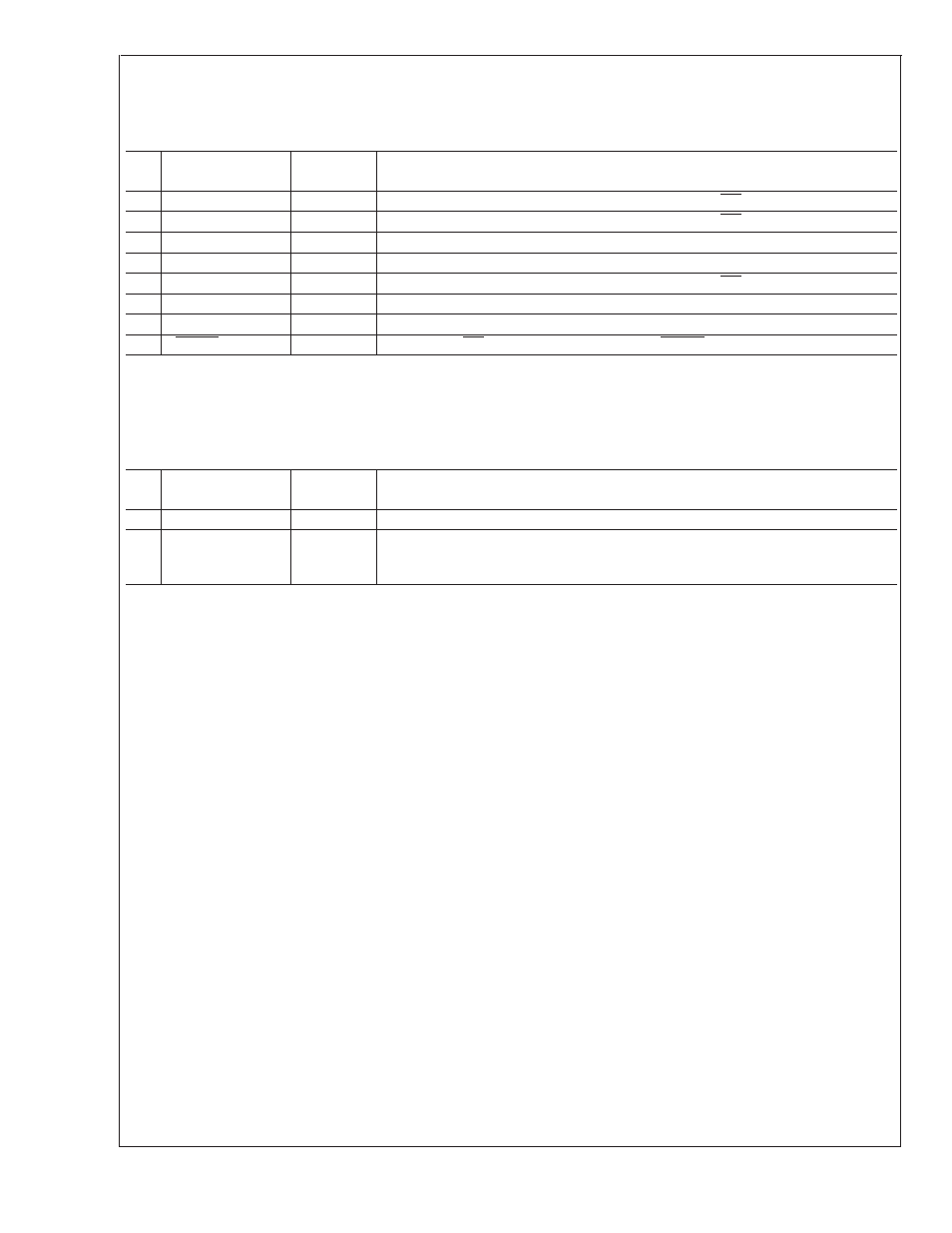

13.7 Interrupt Mask Register 2 — Address 44h

Power on default –

<

7:0

>

= 0000 0000 binary

Bit

Name

Read/

Write

Description

0

+12Vin

Read/Write

A one disables the corresponding interrupt status bit for INT interrupt.

1

Vccp2

Read/Write

A one disables the corresponding interrupt status bit for INT interrupt.

2

Reserved

Read/Write

3

Reserved

Read/Write

4

Chassis Intrusion

Read/Write

A one disables the corresponding interrupt status bit for INT interrupt.

5

Reserved

Read/Write

6

Reserved

Read/Write

7

RESET Enable

Read/Write

<

7

>

= 1 in INT Mask Register 2 enables the RESET in the Configuration Register.

13.8 Reserved Register — Address 45h

Power on default –

<

7:0

>

= 00h. Read/Write for backwards compatibility.

13.9 CI Clear Register — Address 46h

Power on default –

<

7:0

>

= 0000 0000 binary

Bit

Name

Read/

Write

Description

0-6

Reserved

Read/Write

7

CI Clear

Read/Write

A one outputs a minimum 20 ms active low pulse on the Chassis Intrusion pin. The

register bit self clears after the pulse has been output. This bit is mirrored in

Configuration Register bit 6.

LM81

www.national.com

28