Functional description – Rainbow Electronics LM81 User Manual

Page 23

Functional Description

(Continued)

masks for each Interrupt. As described in Section 3.3, the

hardware Interrupt line can also be enabled/disabled in the

Configuration Register.

T_CRIT_A interrupt is dedicated to temperature and is indi-

cated in Extended Mode Register 1. Extended Mode Regis-

ter 1 controls T_CRIT_A.

9.1 Interrupt Clearing

Reading a Status Register will output the contents of the

Register, and reset the Register. A subsequent read done

before the analog “round-robin” monitoring loop is complete

will indicate a cleared Register. Allow at least 820 ms to allow

all Registers to be updated between reads. In summary, the

Interrupt Status Register clears upon being read, and re-

quires at least 400 ms to be updated. When the Interrupt

Status Register clears, the hardware interrupt line will also

clear until the Registers are updated by the monitoring loop.

The hardware Interrupt line (INT) is cleared with the

INT_Clear bit, which is Bit 3 of the Configuration Register.

When this bit is high, the LM81 monitoring loop will stop. It

will resume when the bit is low.

10.0 RESET I/O

RESET is intended to provide a master reset to devices

connected to this line. INT Mask Register 2, Bit 7, must be

set high to enable this function. Setting Bit 4 in the Configu-

ration Register high outputs a least 20 ms low on this line, at

the end of which Bit 4 in the Configuration Register automati-

cally clears. Again, the label for this pin is only its suggested

use. In applications where the RESET capability is not

needed it can be used for any type of digital control that

requires a 20 ms active low open-drain output.

RESET operates as an input when not activated by the

Configuration Register. Setting this line low will reset all of

the registers in the LM81 to their power on default state. All

Value RAM locations will not be affected except for the DAC

Data Register.

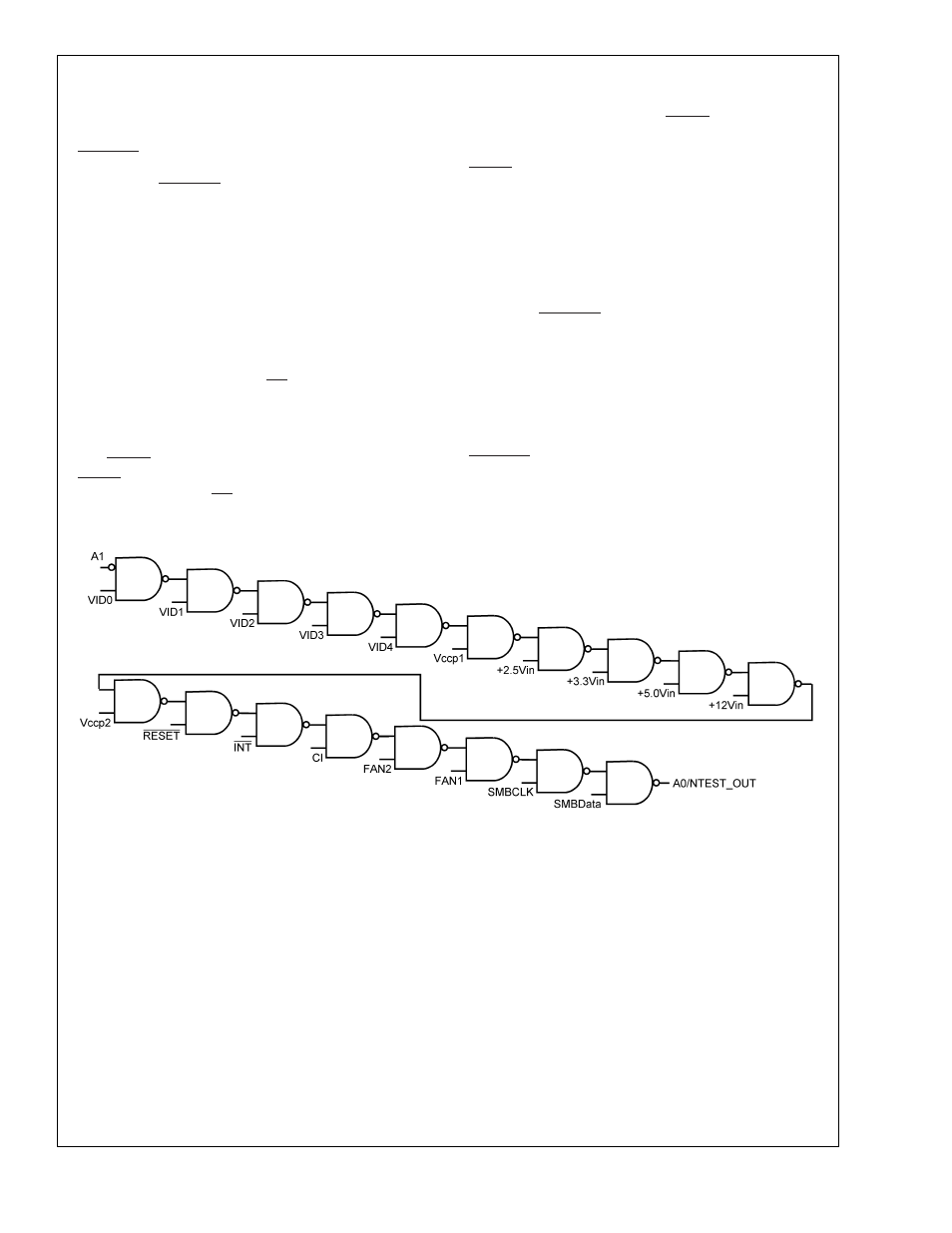

11.0 NAND TREE TESTS

A NAND tree is provided in the LM81 for Automated Test

Equipment (ATE) board level connectivity testing. DACOut/

NTEST_IN, T_CRIT_A, V

+

and GND pins are excluded from

NAND tree testing. Taking DACOut/NTEST_IN high before

the first write to the configuration register activates the

NAND Tree test mode. After the first write to the configura-

tion register the NAND Tree test mode cannot be reacti-

vated. To perform a NAND tree test all pins included in the

NAND tree should be driven to 1 forcing the A0/

NTEST_OUT high. Each individual pin starting with A1 and

concluding with SMBData (excluding DACOut/NTEST_IN,

T_CRIT_A, V

+

and GND) can be taken low with the resulting

toggle observed on the A0/NTEST_OUT pin. Allow for a

typical propagation delay of 500 ns.

DS100072-29

LM81

www.national.com

23