Rainbow Electronics MAX1494 User Manual

Page 5

MAX1492/MAX1494

3.5- and 4.5-Digit, Single-Chip ADCs

with LCD Drivers

_______________________________________________________________________________________

5

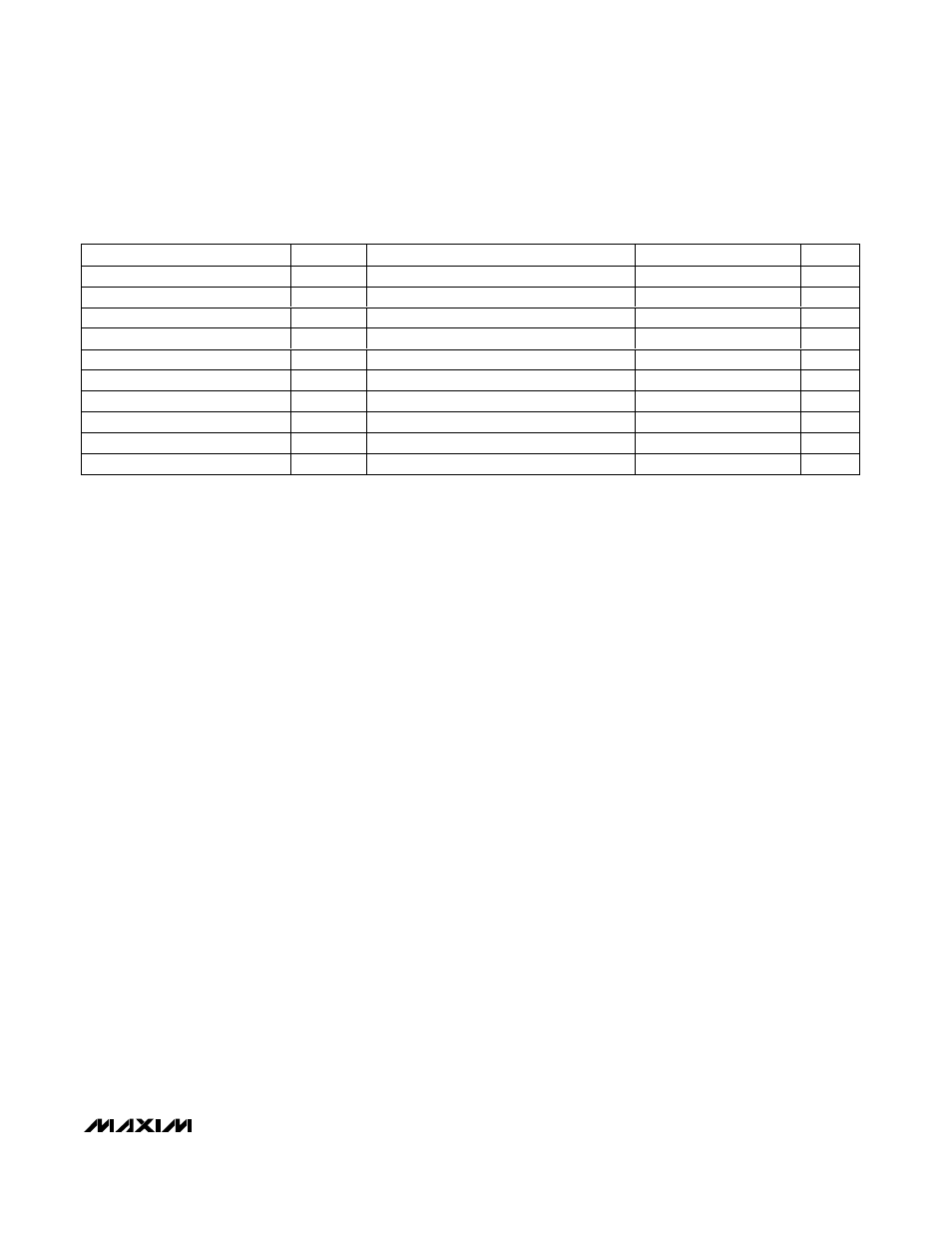

TIMING CHARACTERISTICS (Notes 10, 11 and Figure 13)

(AV

DD

= DV

DD

= 2.7V to +5.25V, GND = 0, T

A

= T

MIN

to T

MAX

, unless otherwise noted.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

SCLK Operating Frequency

f

SCLK

0

4.2

MHz

SCLK Pulse-Width High

t

CH

100

ns

SCLK Pulse-Width Low

t

CL

100

ns

DIN to SCLK Setup

t

DS

50

ns

DIN to SCLK Hold

t

DH

0

ns

CS Fall to SCLK Rise Setup

t

CSS

50

ns

SCLK Rise to CS Rise Hold

t

CSH

0

ns

SCLK Fall to DOUT Valid

t

DO

C

LOAD

= 50pF (Figures 18, 19)

120

ns

CS Rise to DOUT Disable

t

TR

C

LOAD

= 50pF (Figures 18, 19)

120

ns

CS Fall to DOUT Enable

t

DV

C

LOAD

= 50pF (Figures 18, 19)

120

ns

Note 1:

Integral nonlinearity is the deviation of the analog value at any code from its theoretical value after nulling the gain error

and offset error.

Note 2:

Offset calibrated. See the

OFFSET_CAL1 and OFFSET_CAL2 sections in the On-Chip Registers section.

Note 3:

Offset nulled.

Note 4:

Drift error is eliminated by recalibration at the new temperature.

Note 5:

The input voltage range for the analog inputs is given with respect to the voltage on the negative input of the differential pair.

Note 6:

V

AIN+

or V

AIN-

= -2.2V to +2.2V. V

REF+

or V

REF-

= -2.2V to +2.2V. All input structures are identical. Production tested on

AIN+ and REF+ only.

Note 7:

Measured at DC by changing the power-supply voltage from 2.7V to 5.25V and measuring the effect on the conversion

error with external reference. PSRR at 50Hz and 60Hz exceeds 120dB with filter notches at 50Hz and 60Hz (Figure 2).

Note 8:

CLK and SCLK are idle.

Note 9:

Power-supply currents are measured with all digital inputs at either GND or DV

DD

and with the device in internal clock mode.

Note 10: All input signals are specified with t

RISE

= t

FALL

= 5ns (10% to 90% of DV

DD

) and are timed from a voltage level of 50% of

DV

DD

, unless otherwise noted.

Note 11: See the serial-interface timing diagrams.