Detailed description, Pseudo-differential input, Track/hold – Rainbow Electronics MAX1249 User Manual

Page 8

MAX1248/MAX1249

+2.7V to +5.25V, Low-Power, 4-Channel,

Serial 10-Bit ADCs in QSOP-16

8

_______________________________________________________________________________________

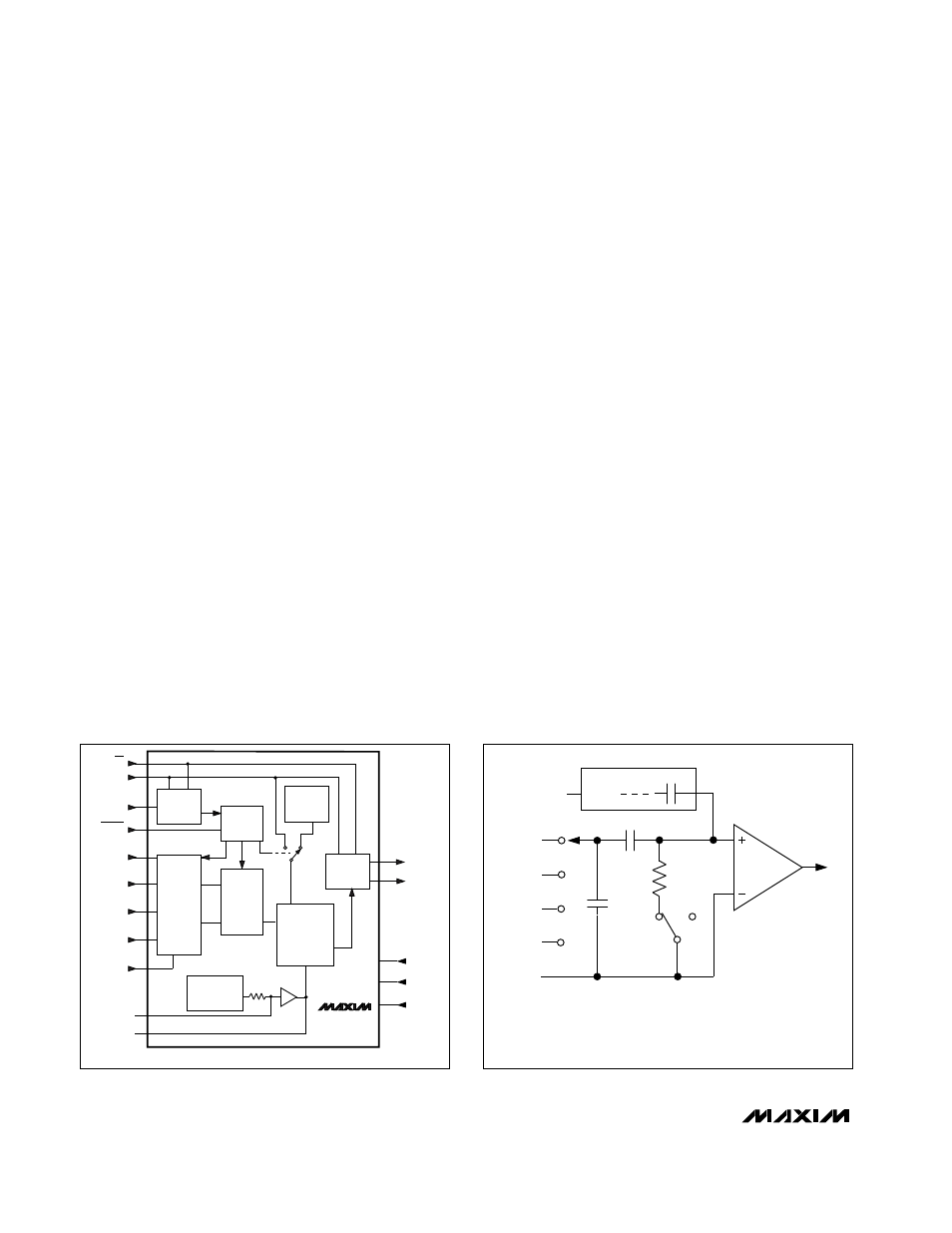

_______________Detailed Description

The MAX1248/MAX1249 analog-to-digital converters

(ADCs) use a successive-approximation conversion

technique and input track/hold (T/H) circuitry to convert

an analog signal to a 10-bit digital output. A flexible

serial interface provides easy interface to microproces-

sors (µPs). Figure 3 is a block diagram of the

MAX1248/MAX1249.

Pseudo-Differential Input

The sampling architecture of the ADC’s analog com-

parator is illustrated in the equivalent input circuit

(Figure 4). In single-ended mode, IN+ is internally

switched to CH0–CH3, and IN- is switched to COM. In

differential mode, IN+ and IN- are selected from two

pairs: CH0/CH1 and CH2/CH3. Configure the channels

with Tables 2 and 3. Please note that the codes for

CH0–CH3 in the MAX1248/MAX1249 correspond to

the codes for CH2–CH5 in the eight-channel

(MAX148/MAX149) versions.

In differential mode, IN- and IN+ are internally switched

to either of the analog inputs. This configuration is

pseudo-differential to the effect that only the signal at

IN+ is sampled. The return side (IN-) must remain sta-

ble within ±0.5LSB (±0.1LSB for best results) with

respect to AGND during a conversion. To accomplish

this, connect a 0.1µF capacitor from IN- (the selected

analog input) to AGND.

During the acquisition interval, the channel selected as

the positive input (IN+) charges capacitor C

HOLD

. The

acquisition interval spans three SCLK cycles and ends

on the falling SCLK edge after the last bit of the input

control word has been entered. At the end of the acqui-

sition interval, the T/H switch opens, retaining charge

on C

HOLD

as a sample of the signal at IN+.

The conversion interval begins with the input multiplex-

er switching C

HOLD

from the positive input (IN+) to the

negative input (IN-). In single-ended mode, IN- is sim-

ply COM. This unbalances node ZERO at the compara-

tor’s input. The capacitive DAC adjusts during the

remainder of the conversion cycle to restore node

ZERO to 0V within the limits of 10-bit resolution. This

action is equivalent to transferring a charge of 16pF x

[(V

IN

+

) - (V

IN

-)] from C

HOLD

to the binary-weighted

capacitive DAC, which in turn forms a digital represen-

tation of the analog input signal.

Track/Hold

The T/H enters its tracking mode on the falling clock

edge after the fifth bit of the 8-bit control word has been

shifted in. It enters its hold mode on the falling clock

edge after the eighth bit of the control word has been

shifted in. If the converter is set up for single-ended

inputs, IN- is connected to COM, and the converter

samples the “+” input. If the converter is set up for dif-

ferential inputs, IN- connects to the “-” input, and the

difference of

|

IN+ - IN-

|

is sampled. At the end of the

conversion, the positive input connects back to IN+,

and C

HOLD

charges to the input signal.

The time required for the T/H to acquire an input signal

is a function of how quickly its input capacitance is

charged. If the input signal’s source impedance is high,

INPUT

SHIFT

REGISTER

CONTROL

LOGIC

INT

CLOCK

OUTPUT

SHIFT

REGISTER

+1.21V

REFERENCE

(MAX1248)

T/H

ANALOG

INPUT

MUX

SAR

ADC

IN

DOUT

SSTRB

V

DD

DGND

AGND

SCLK

DIN

COM

REFADJ

VREF

OUT

REF

CLOCK

+2.500V

20k

A

≈

2.06*

*A

≈

2.00 (MAX1249)

7

8

9

6

12

13

14

15

16

CH3

5

CH2

4

CH1

3

CH0

2

MAX1248

MAX1249

CS

SHDN

1

11

10

Figure 3. Block Diagram

CH0

CH1

CH2

CH3

COM

C

SWITCH

TRACK

T/H

SWITCH

R

IN

9k

C

HOLD

HOLD

CAPACITIVE DAC

VREF

ZERO

COMPARATOR

–

+

16pF

SINGLE-ENDED MODE: IN+ = CHO–CH3, IN- = COM.

DIFFERENTIAL MODE: IN+ AND IN- SELECTED FROM PAIRS OF

CH0/CH1 AND CH2/CH3.

AT THE SAMPLING INSTANT,

THE MUX INPUT SWITCHES

FROM THE SELECTED IN+

CHANNEL TO THE SELECTED

IN- CHANNEL.

INPUT

MUX

Figure 4. Equivalent Input Circuit