Applications information – Rainbow Electronics MAX1113 User Manual

Page 16

__________Applications Information

Power-On Reset

When power is first applied, and if SHDN is not pulled

low, internal power-on reset circuitry activates the

MAX1112/MAX1113 in internal clock mode. SSTRB is

high on power-up and, if CS is low, the first logical 1 on

DIN is interpreted as a start bit. Until a conversion takes

place, DOUT shifts out zeros. No conversions should

be performed until the reference voltage has stabilized

(see the Wakeup Time specifications in the

Timing

Characteristics

).

Power-Down

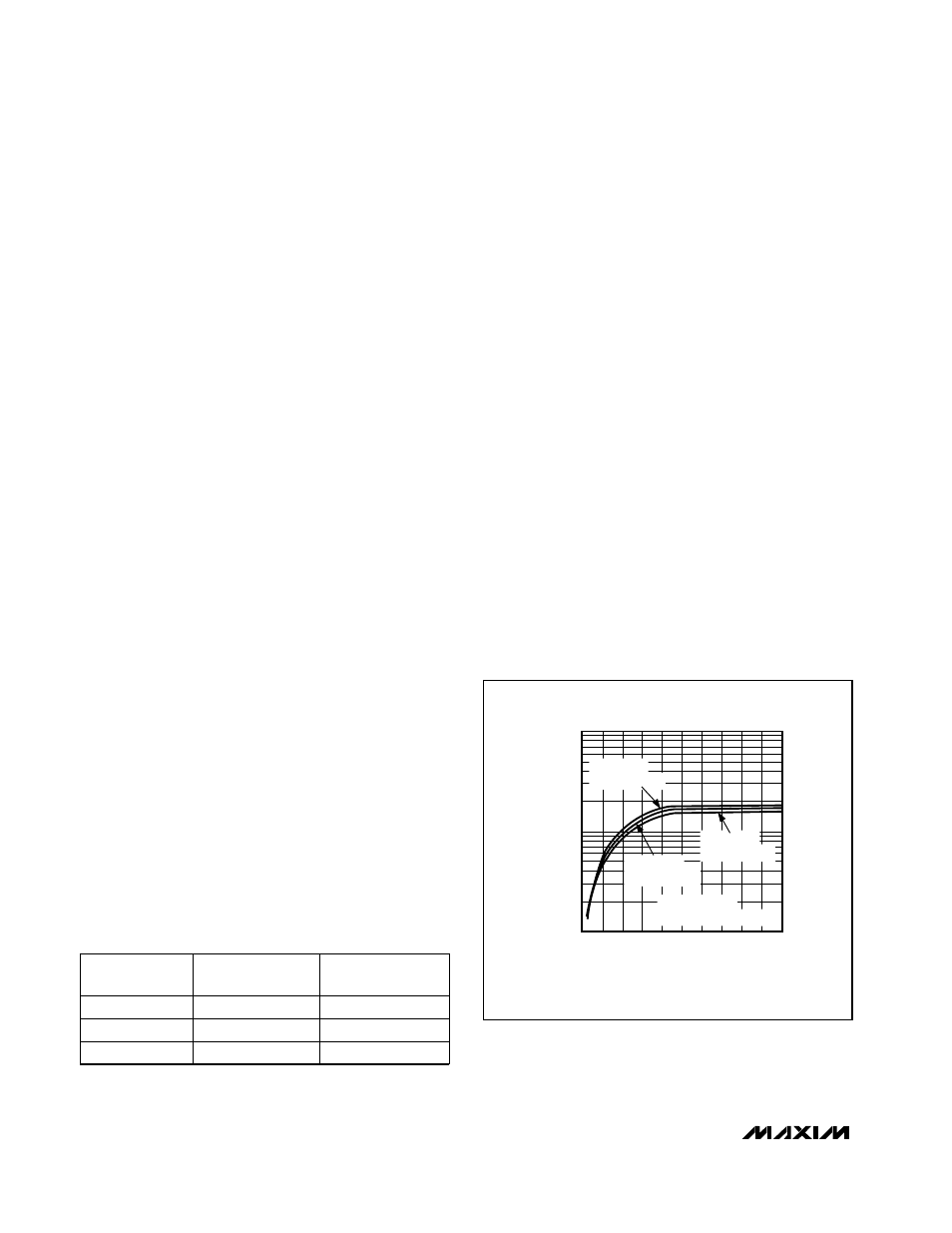

When operating at speeds below the maximum sam-

pling rate, the MAX1112/MAX1113’s automatic power-

down mode can save considerable power by placing

the converters in a low-current shutdown state between

conversions. Figure 13 shows the average supply cur-

rent as a function of the sampling rate.

Select power-down with PD1 of the DIN control byte

with SHDN high or floating (Table 3). Pull SHDN low at

any time to shut down the converters completely. SHDN

overrides PD1 of the control byte. Figures 14a and 14b

illustrate the various power-down sequences in both

external and internal clock modes.

Software Power-Down

Software power-down is activated using bit PD1 of the

control byte. When software power-down is asserted, the

ADCs continue to operate in the last specified clock

mode until the conversion is complete. The ADCs then

power down into a low quiescent-current state. In internal

clock mode, the interface remains active, and conversion

results may be clocked out after the MAX1112/

MAX1113 have entered a software power-down.

The first logical 1 on DIN is interpreted as a start bit,

which powers up the MAX1112/MAX1113. If the DIN byte

contains PD1 = 1, then the chip remains powered up. If

PD1 = 0, power-down resumes after one conversion.

Hard-Wired Power-Down

Pulling SHDN low places the converters in hard-wired

power-down. Unlike software power-down, the conver-

sion is not completed; it stops coincidentally with SHDN

being brought low. SHDN also controls the state of the

internal reference (Table 5). Letting SHDN float enables

the internal 4.096V voltage reference. When returning to

normal operation with SHDN floating, there is a t

RC

delay of approximately 1M

Ω

x C

LOAD

, where C

LOAD

is

the capacitive loading on the SHDN pin. Pulling SHDN

high disables the internal reference, which saves power

when using an external reference.

External Reference

An external reference between 1V and V

DD

should be

connected directly at the REFIN terminal. The DC input

impedance at REFIN is extremely high, consisting of

leakage current only (typically 10nA). During a conver-

sion, the reference must be able to deliver up to 20µA

average load current and have an output impedance of

1k

Ω

or less at the conversion clock frequency. If the

reference has higher output impedance or is noisy,

bypass it close to the REFIN pin with a 0.1µF capacitor.

If an external reference is used with the MAX1112/

MAX1113, tie SHDN to V

DD

to disable the internal refer-

ence and decrease power consumption.

MAX1112/MAX1113

+5V, Low-Power, Multi-Channel,

Serial 8-Bit ADCs

16

______________________________________________________________________________________

Table 5. Hard-Wired Power-Down and

Internal Reference State

SHDN

STATE

DEVICE

MODE

1

Enabled

Floating

Enabled

0

Power-Down

INTERNAL

REFERENCE

Disabled

Disabled

Enabled

1000

10

0

10

30

50

100

MAX1112/13-fig13

SAMPLING RATE (ksps)

SUPPLY CURRENT (

µ

A)

20

40

V

DD

= V

REFIN

= 5V

C

LOAD

AT DOUT + SSTRB

C

LOAD

= 30pF

CODE = 11111111

C

LOAD

= 30pF

CODE = 10101010

C

LOAD

= 60pF

CODE = 10101010

Figure 13. Average Supply Current vs. Sampling Rate