Pin description – Rainbow Electronics MAX1215 User Manual

Page 8

MAX1215

1.8V, 12-Bit, 250Msps ADC for

Broadband Applications

8

_______________________________________________________________________________________

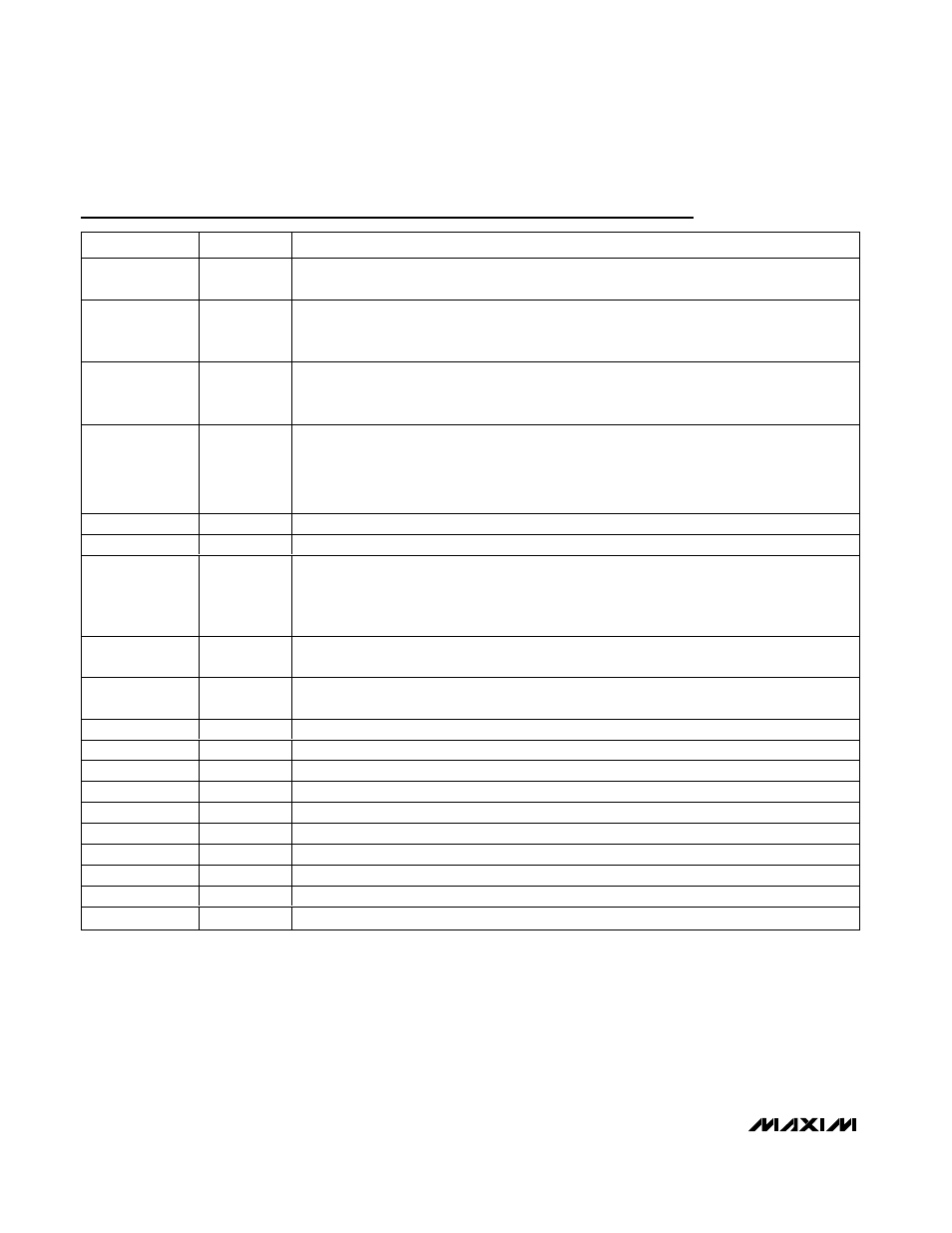

Pin Description

PIN

NAME

FUNCTION

1, 6, 11–14, 20,

25, 62, 63, 65

AV

CC

Analog Supply Voltage. Bypass each pin with a parallel combination of 0.1µF and 0.22µF

capacitors for best decoupling results.

2, 5, 7, 10, 15, 16,

18, 19, 21, 24,

64, 66, 67

AGND

Analog Converter Ground

3

REFIO

Reference Input/Output. With REFADJ pulled high, this I/O port allows an external reference

source to be connected to the MAX1215. With REFADJ pulled low, the internal 1.23V bandgap

reference is active.

4

REFADJ

Reference Adjust Input. REFADJ allows for FSR adjustments by placing a resistor or trim

potentiometer between REFADJ and AGND (decreases FSR) or REFADJ and REFIO (increases

FSR). If REFADJ is connected to AV

CC

, the internal reference can be overdriven with an

external source connected to REFIO. If REFADJ is connected to AGND, the internal reference is

used to determine the FSR of the data converter.

8

INP

Positive Analog Input Terminal. Internally self-biased to 1.365V.

9

INN

Negative Analog Input Terminal. Internally self-biased to 1.365V.

17

CLKDIV

Clock Divider Input. This LVCMOS-compatible input controls with which speed the converter’s

digital outputs are updated. CLKDIV has an internal pulldown resistor.

CLKDIV = 0: ADC updates digital outputs at one-half the input clock rate.

CLKDIV = 1: ADC updates digital outputs at input clock rate.

22

CLKP

True Clock Input. This input ideally requires an LVPECL-compatible input level to maintain the

converter’s excellent performance. Internally self-biased to 1.15V.

23

CLKN

Complementary Clock Input. This input ideally requires an LVPECL-compatible input level to

maintain the converter’s excellent performance. Internally self-biased to 1.15V.

26, 45, 61

OGND

Digital Converter Ground. Ground connection for digital circuitry and output drivers.

27, 28, 41, 44, 60

OV

CC

Digital Supply Voltage. Bypass with a 0.1µF capacitor for best decoupling results.

29

D0N

Complementary Output Bit 0 (LSB)

30

D0P

True Output Bit 0 (LSB)

31

D1N

Complementary Output Bit 1

32

D1P

True Output Bit 1

33

D2N

Complementary Output Bit 2

34

D2P

True Output Bit 2

35

D3N

Complementary Output Bit 3

36

D3P

True Output Bit 3