Rainbow Electronics MAX1471 User Manual

Page 21

ing once t

CPU

has expired. At the beginning of t

RF

, the

modules selected in the power control register (register

0x0) are powered up with the exception of the peak

detectors and have the t

RF

period to settle.

At the end of t

RF

, the MAX1471 stops driving DIO low

and enables ADATA, FDATA, and peak detectors if

chosen to be active in the power configuration register

(0x0). The CPU must be awake at this point, and must

hold DIO low for the MAX1471 to remain in operation.

The CPU must begin driving DIO low any time during

t

LOW

= t

CPU

+ t

RF

. If the CPU fails to drive DIO low,

DIO is pulled high through the internal pullup resistor,

and the timer sequence is restarted, leaving the

MAX1471 powered down. Any time the DIO line is dri-

ven high while the DRX = 1, the DRX sequence is initi-

ated, as defined in Figure 12.

t

RF

is a 16-bit timer, configured through registers 0x7

(upper byte) and 0x8 (lower byte). The possible t

RF

set-

tings are in Table 12. The data written to the t

RF

register

(0x7 and 0x8) is multiplied by 120µs to give the total t

RF

time. On power-up, the RF timer registers are set to

zero and must be written before using DRX mode.

Typical Power-Up Procedure

Here is a typical power-up procedure for receiving either

ASK or FSK signals at 315MHz in continuous mode:

1) Write 0x3000 to reset the part.

2) Write 0x10FE to enable all RF and baseband sections.

3) Write 0x135F to set the oscillator frequency register

to work with a 315MHz crystal.

4) Write 0x1120 to set FSKCALLSB for an accurate

FSK calibration.

5) Write 0x1201 to begin FSK calibration.

6) Read 0x2900 and verify that bit 0 is 1 to indicate

FSK calibration is done.

The MAX1471 is now ready to receive ASK or FSK data.

Due to the high sensitivity of the receiver, it is recom-

mended that the configuration registers be changed

only when not receiving data. Receiver desensitization

may occur, especially if odd-order harmonics of the

SCLK line fall within the IF bandwidth.

MAX1471

315MHz/434MHz Low-Power, 3V/5V

ASK/FSK Superheterodyne Receiver

______________________________________________________________________________________

21

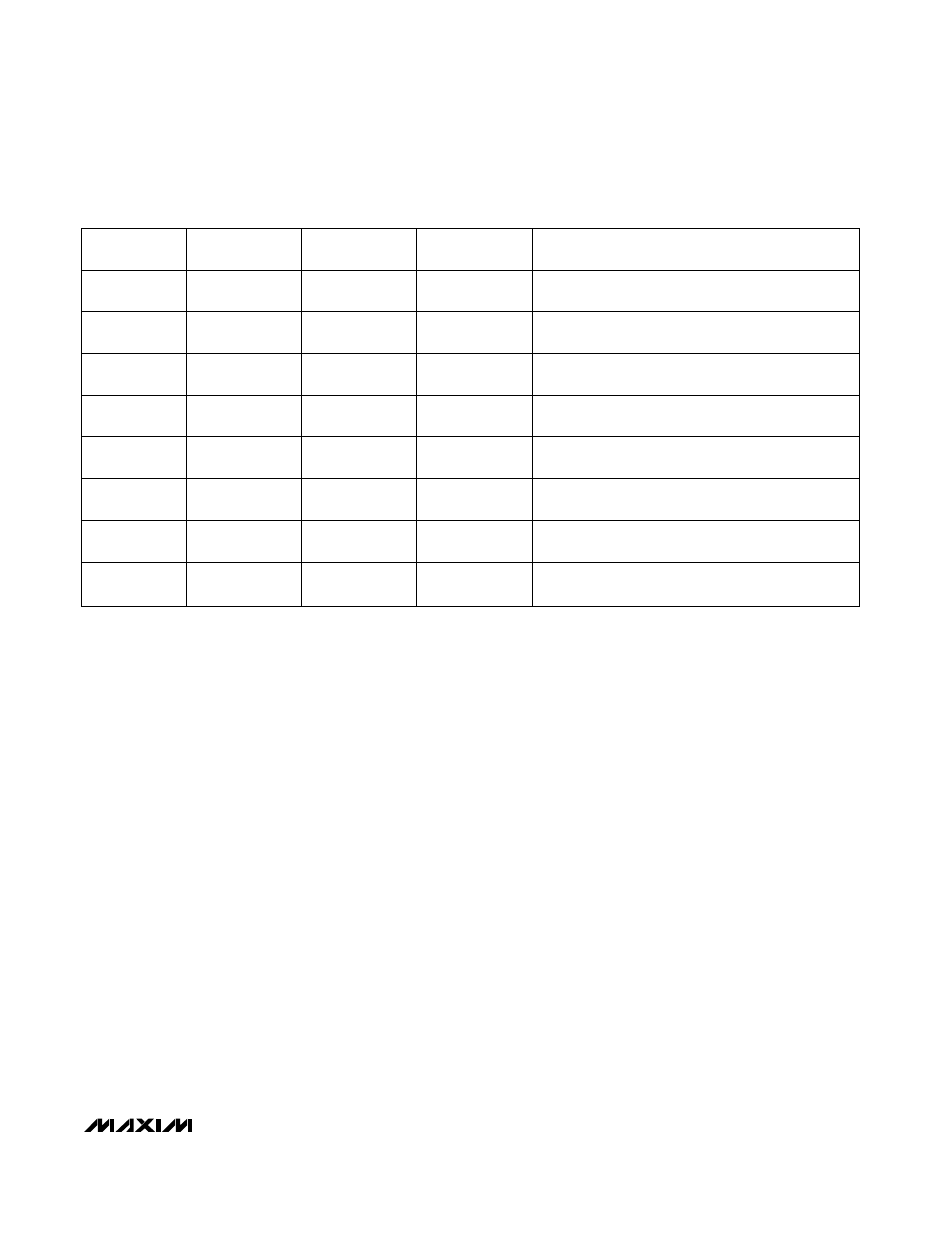

Table 6. Power Configuration Register (Address: 0x0)

BIT ID

BIT NAME

BIT LOCATION

(0 = LSB)

POWER-UP

STATE

FUNCTION

LNA_EN

LNA enable

7

0

1 = Enable LNA

0 = Disable LNA

AGC_EN

AGC enable

6

0

1 = Enable AGC

0 = Disable AGC

MIXER_EN

Mixer enable

5

0

1 = Enable mixer

0 = Disable mixer

FSKBB_EN

FSK baseband

enable

4

0

1 = Enable FSK baseband

0 = Disable FSK baseband

FSKPD_EN

FSK peak

detector enable

3

0

1 = Enable FSK peak detectors

0 = Disable FSK peak detectors

ASKBB_EN

ASK baseband

enable

2

0

1 = Enable ASK baseband

0 = Disable ASK baseband

ASKPD_EN

ASK peak

detector enable

1

0

1 = Enable ASK peak detectors

0 = Disable ASK peak detectors

SLEEP

Sleep mode

0

0

1 = Deep-sleep mode

0 = Normal operation