Max1121 – Rainbow Electronics MAX1121 User Manual

Page 12

MAX1121

Divide-by-2 Clock Control (CLKDIV)

The MAX1121 offers a clock control line (CLKDIV),

which supports the reduction of clock jitter in a system.

Connect CLKDIV to OGND to enable the ADC’s internal

divide-by-2 clock divider. Data is now updated at one-

half the ADC’s input clock rate. CLKDIV has an internal

pulldown resistor and can be left open for applications

that only operate with update rates one-half of the con-

verter’s sampling rate. Connecting CLKDIV to OV

CC

allows data to be updated at the speed of the ADC input

clock.

System Timing Requirements

Figure 4 depicts the relationship between the clock

input and output, analog input, sampling event, and

data output. The MAX1121 samples on the rising

(falling) edge of CLKP (CLKN). Output data is valid on

the next rising (falling) edge of the DCLKP (DCLKN)

clock, but has an internal latency of nine clock cycles.

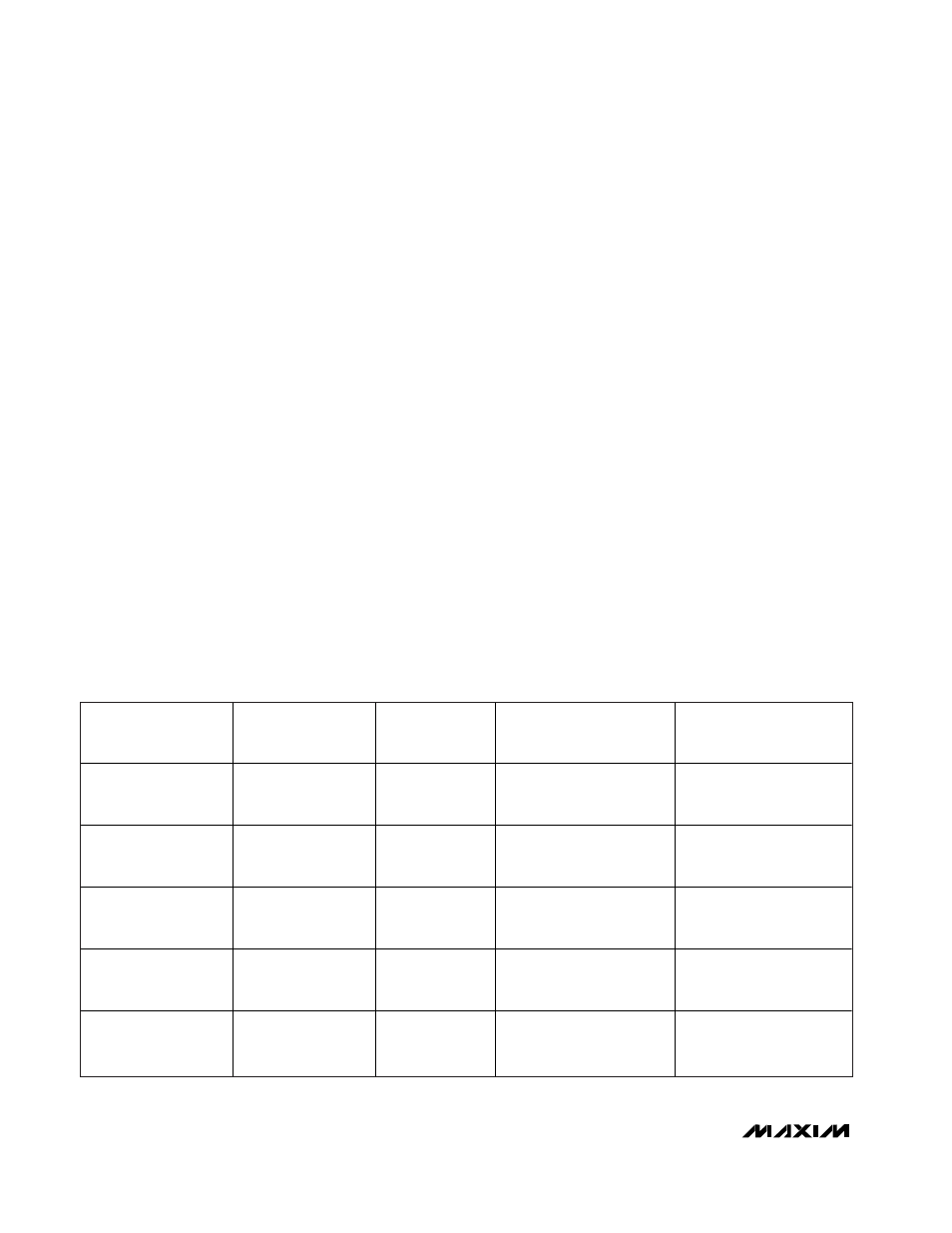

Digital Outputs (D0P/N–D7P/N, DCLKP/N,

ORP/N) and Control Input

T

/B

The digital outputs D0P/N–D7P/N, DCLKP/N, and ORP/N

are LVDS compatible, and data on D0P/N–D7P/N is pre-

sented in either binary or two’s complement format (Table

1). The

T/B control line is an LVCMOS-compatible input,

which allows the user to select the desired output for-

mat. Pulling

T/B low outputs data in two’s complement

and pulling it high presents data in offset binary format

on the 10-bit parallel bus.

T/B has an internal pulldown

resistor and may be left unconnected in applications

using only two’s complement output format. All LVDS

outputs provide a typical voltage swing of 0.4V around

a common-mode voltage of approximately 1.2V, and

must be terminated at the far end of each transmission

line pair (true and complementary) with 100Ω. The

LVDS outputs are powered from a separate power sup-

ply, which can be operated between 1.7V and 1.9V.

The MAX1121 offers an additional differential output

pair (ORP, ORN) to flag out-of-range conditions, where

out of range is above positive or below negative full

scale. An out-of-range condition is identified with ORP

(ORN) transitioning high (low).

Note: Although differential LVDS reduces single-ended

transients to the supply and ground planes, capacitive

loading on the digital outputs should still be kept as low

as possible. Using LVDS buffers on the digital outputs

of the ADC when driving off-board may improve overall

performance and reduce system timing constraints.

1.8V, 8-Bit, 250Msps Analog-to-Digital Converter

with LVDS Outputs for Wideband Applications

12

______________________________________________________________________________________

INP ANALOG

VOLTAGE LEVEL

INN ANALOG

VOLTAGE LEVEL

OUT-OF-RANGE

ORP (ORN)

BINARY

DIGITAL OUTPUT CODE

(D7–D0)

TWO’S COMPLEMENT

DIGITAL OUTPUT CODE

(D7–D0)

> V

CM

+ 0.3125V

< V

CM

- 0.3125V

1 (0)

1111 1111

(exceeds positive full scale,

OR set)

0111 1111

(exceeds positive full scale,

OR set)

V

CM

+ 0.3125V

V

CM

- 0.3125V

0 (1)

1111 1111

(represents positive full

scale)

0111 1111

(represents positive full

scale)

V

CM

V

CM

0 (1)

1000 0000 or

0111 1111

(represents midscale)

0000 0000 or

1111 1111

(represents midscale)

V

CM

- 0.3125V

V

CM

+ 0.3125V

0 (1)

0000 0000

(represents negative full

scale)

1000 0000

(represents negative full

scale)

< V

CM

- 0.3125V

> V

CM

+ 0.3125V

1 (0)

0000 0000

(exceeds negative full scale,

OR set)

1000 0000

(exceeds negative full scale,

OR set)

Table 1. MAX1121 Digital Output Coding