Electrical characteristics (continued) – Rainbow Electronics MAX769 User Manual

Page 3

MAX769

2 or 3-Cell, Step-Up/Down,

Two-Way Pager System IC

_______________________________________________________________________________________

3

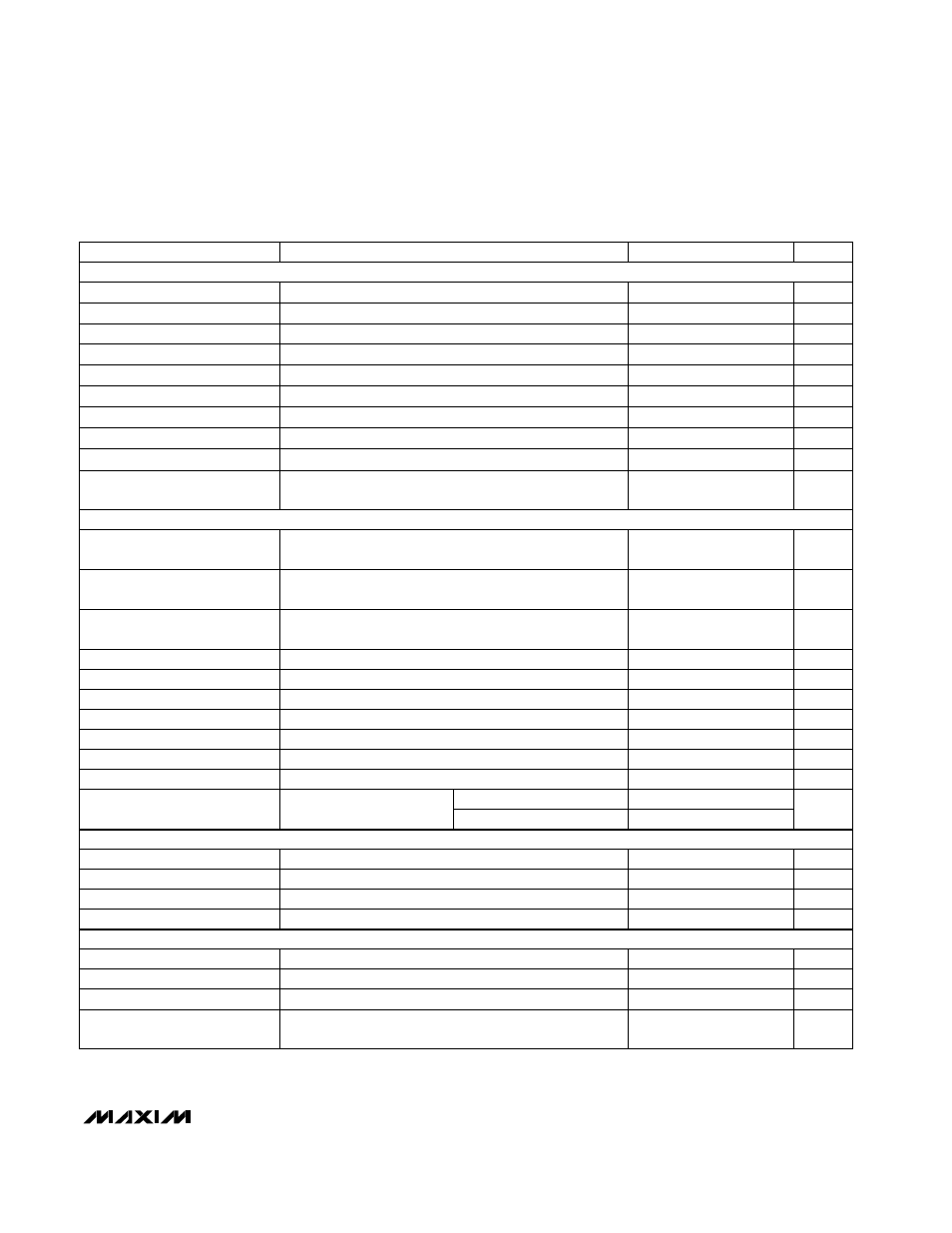

ELECTRICAL CHARACTERISTICS (continued)

(OUT = 3.0V, BATT = 3.6V, T

A

= -40°C to +85°C, unless otherwise noted. Typical values are at T

A

= +25°C.) (Note 1)

%

-3.5

3.5

OUT Error, Coast Mode

(Note 11)

%

Coast Mode, OUT = 1.8V to 4.9V

-3.5

3.5

OUT Error, Run Mode (Note 12)

Circuit of Figure 2, OUT = 3.0V, BATT = 3.0V

Run Mode, OUT = 1.8V to 4.9V

Circuit of Figure 2, OUT = 3.0V, BATT = 3.0V

CONDITIONS

BATT = 1.6V to 4.5V

mV

25

OUT Line Regulation

I

OUT

= 80mA, C

OUT

= 47µF with ESR < 0.25

Ω

mVp-p

70

OUT Voltage Ripple

LX1, LX2, BATT = 3.0V

Ω

0.9

1.8

LX On-Resistance (Note 14)

ns

50

ns

50

CS to SCL Hold Time (t

CSH

)

CS to SCL Setup Time (t

CSS

)

ns

100

SDI Setup Time (t

DS

)

NMOS

PMOS

1.3

2.6

T

A

= +25°C, FILT connected to REF

kHz

210

270

325

Frequency, Free-Run

Backup Mode, NICD = 3.3V

f

SYNC

= 38.4kHz

ns

100

kHz

CS Pulse Width High (t

CSW

)

268.8

ns

70

Frequency, Locked

CS to SDO Disable (t

TR

)

Ω

f

SYNC

= 38.4kHz, FILT Network = 1nF

(22nF + 10k

Ω

)

kHz

±15

Jitter (Note 15)

5

10

f

SYNC

= 38.4kHz, FILT Network = 1nF

(22nF + 10k

Ω

)

ms

1

25

Capture Time (Note 15)

Backup-Regulator

On-Resistance (Note 16)

ns

50

0.2V < (OUT - NICD) < 2V, 15mA_CHG = 1

SCL Pulse Width High or Low

(t

CH

, t

CL

)

mA

mA

80

115

7

25

Output Current, Run Mode

(Note 10)

mA

15

40

Current High

Output Current, Coast Mode

(Note 10)

UNITS

MIN

TYP

MAX

PARAMETER

0.2V < (OUT - NICD) < 2V, 1mA_CHG = 1

mA

0.45

1.5

Current Low

OUT = 2.8V, I

OUT

= 20mA, NICD = 3.3V

%

-3.5

3.5

OUT Error, Backup Regulator

50% duty cycle

MHz

5

SCL Maximum Clock Rate

OUT = 3.0V

%

76

83

Maximum LX Duty Cycle

During the inductor charge cycle

mA

300

350

400

LX Switch Current Limit

ns

70

ns

70

CS to SDO Output Valid (t

DV

)

SCL to SDO Output Valid (t

DO

)

ns

50

SDI Hold Time (t

DH

)

I

OUT

= 1mA to 80mA, Run Mode

mV

25

OUT Load Regulation

Coast or Run Mode, OUT = 1.8V to 4.9V

mV

30

100

170

OUT DAC Step Size (Note 13)

SERIAL-INTERFACE TIMING SPECIFICATIONS

(Note 9)

DC-DC CONVERTER

PHASE-LOCKED LOOP (PLL)

NICD CHARGER