Table 7. detailed sspcon register contents, Pic16 with ssp module and pic17 interface – Rainbow Electronics MAX1068 User Manual

Page 25

MAX1067/MAX1068

Multichannel, 14-Bit, 200ksps Analog-to-Digital

Converters

______________________________________________________________________________________

25

QSPI Interface

Using the high-speed QSPI interface with CPOL = 0

and CPHA = 0, the MAX1067/MAX1068 support a

maximum f

SCLK

of 4.8MHz. Figure 21a shows the

MAX1067/MAX1068 connected to a QSPI master and

Figure 21b shows the associated interface timing.

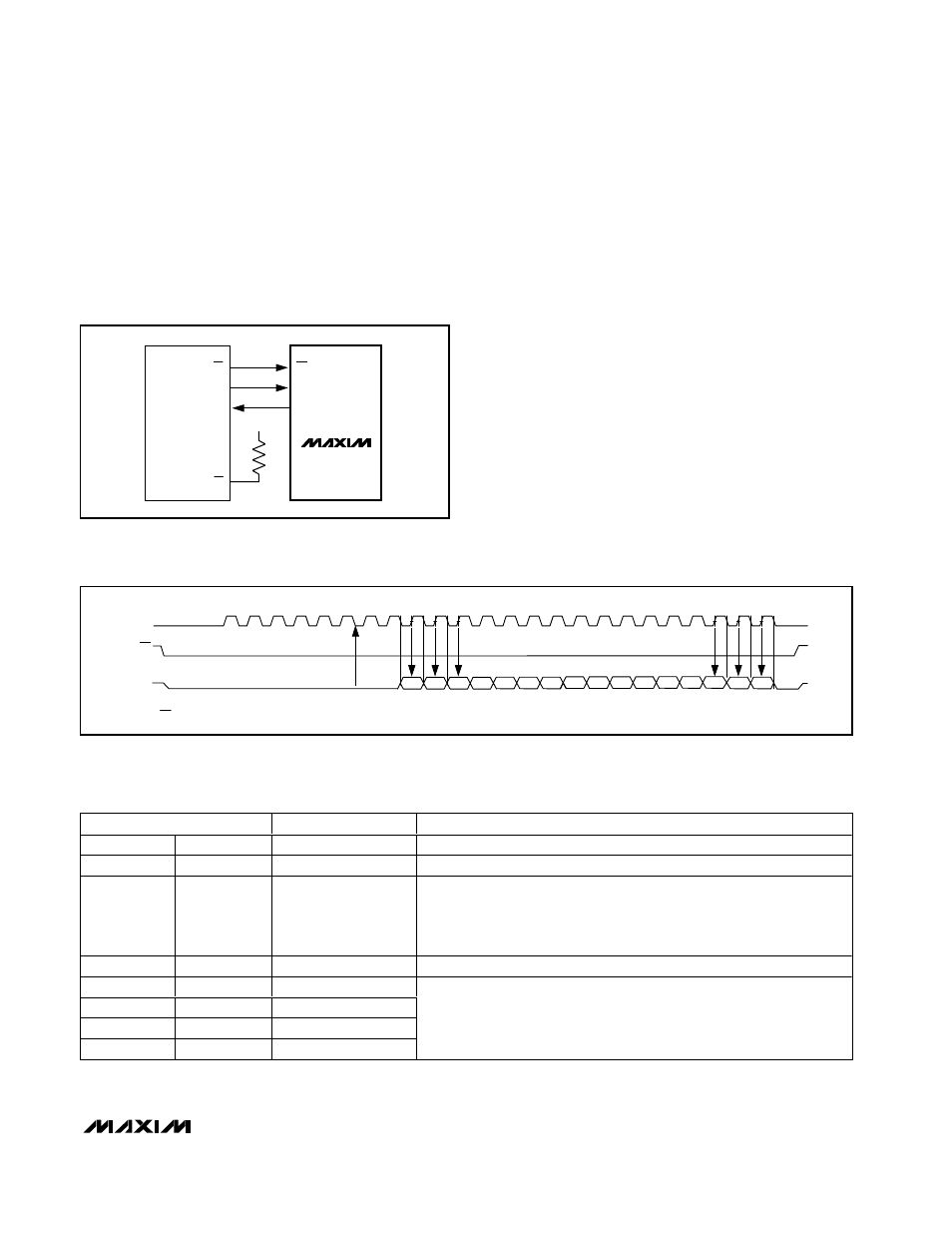

PIC16 with SSP Module and PIC17

Interface

The MAX1067/MAX1068 are compatible with a PIC16/

PIC17 controller (µC), using the synchronous serial-port

(SSP) module.

To establish SPI communication, connect the controller

as shown in Figure 22a and configure the PIC16/PIC17

as system master by initializing its synchronous serial-

port control register (SSPCON) and synchronous serial-

port status register (SSPSTAT) to the bit patterns shown

in Tables 7 and 8.

In SPI mode, the PIC16/PIC17 µCs allow 8 bits of data to

be synchronously transmitted and received simultane-

ously. Three consecutive 8-bit-wide readings (Figure

22b) are necessary to obtain the entire 14-bit result from

the ADC. DOUT data transitions on the serial clock’s

falling edge and is clocked into the µC on SCLK’s rising

edge. The first 8-bit-wide data stream contains all zeros.

The 2nd 8-bit-wide data stream contains the MSB

through D6. The 3rd 8-bit-wide data stream contains bits

D5 through D0 followed by S1 and S0.

DOUT*

CS

SCLK

*WHEN CS IS HIGH, DOUT = HIGH-Z

MSB

20

16

D13

D12

D11

D10

D9

D8

D7

HIGH-Z

S1

S0

24

12

1

4

8

6

D6

D3

D2

D1

LSB

D5

D4

SAMPLING INSTANT

D0

Figure 21b. QSPI Interface Timing Sequence (External Clock, 8-Bit Data Transfer, CPOL = CPHA = 0)

CONTROL BIT

SETTINGS

SYNCHRONOUS SERIAL-PORT CONTROL REGISTER (SSPCON)

WCOL

BIT7

X

Write Collision Detection Bit

SSPOV

BIT6

X

Receive Overflow Detection Bit

SSPEN

BIT5

1

Synchronous Serial-Port Enable Bit:

0: Disables serial port and configures these pins as I/O port pins.

1: Enables serial port and configures SCK, SDO, and SCI pins as serial

port pins.

CKP

BIT4

0

Clock Polarity Select Bit. CKP = 0 for SPI master-mode selection.

SSPM3

BIT3

0

SSPM2

BIT2

0

SSPM1

BIT1

0

SSPM0

BIT0

1

Synchronous Serial-Port Mode Select Bit. Sets SPI master-mode and

selects f

CLK

= f

OSC

/ 16.

Table 7. Detailed SSPCON Register Contents

X = Don’t care.

QSPI

SCLK

DOUT

CS

SCK

MISO

V

DD

SS

CS

MAX1067

MAX1068

Figure 21a. QSPI Connections