Ds1372, C, 32-bit, binary counter clock with 64-bit id, Alarm operation – Rainbow Electronics DS1372 User Manual

Page 6

DS1372

Alarm Operation

The alarm counter is a 24-bit counter in the address

range 04h–06h. When the alarm counter is written, a

seed register is written with the alarm counter value.

When the alarm counter enable (ACE) bit in the Control

Register is set to 1, the counter begins counting down

from the seed value. When the counter reaches zero, it

sets the AF bit in the Status Register, if the AF bit is not

already set. If the AIE and INTCN bits are both set to a

logic 1, the SQW/INT pin goes low and remains low

until AF is written to logic 0. The counter is then

reloaded with the seed value and the countdown

restarts. When the counter is read, the current counter

value is latched into a register, which is output on the

serial data line while the counter continues to decre-

ment. The counter is disabled if the seed value is zero

or if ACE = 0. Whenever the ACE is set from 0 to 1, the

counter is reloaded with the current seed value and the

counter begins to count down. Note: When initializing

or changing the alarm value, the ACE bit should be

enabled after writing the alarm counter bytes.

6

_______________________________________________________________________________________

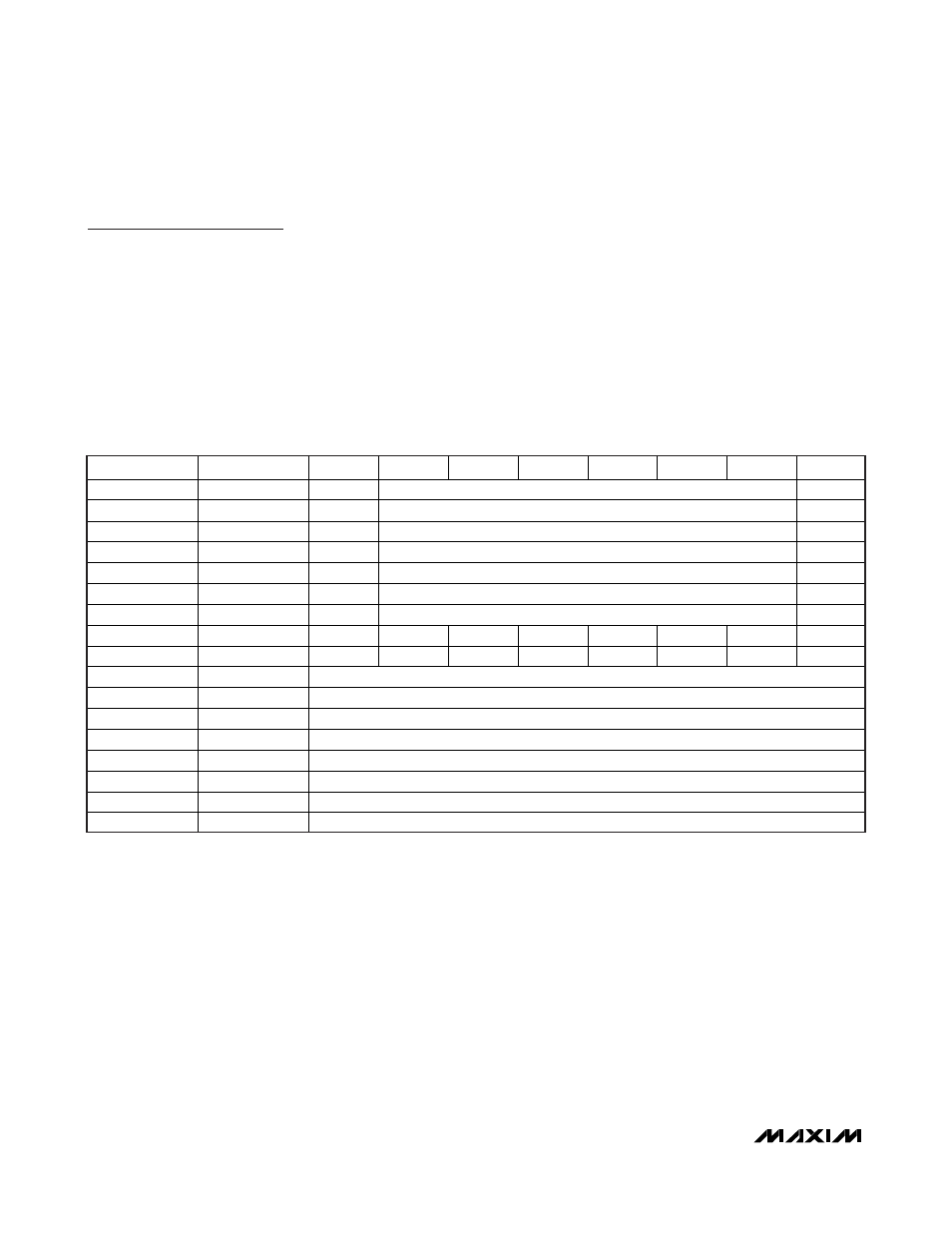

ADDRESS

REGISTER

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

00h

Clock

—

Seconds Counter Byte 0

LSB

01h

Clock

—

Seconds Counter Byte 1

—

02h

Clock

—

Seconds Counter Byte 2

—

03h

Clock

MSB

Seconds Counter Byte 3

—

04h

Alarm

—

Alarm Counter Byte 0

LSB

05h

Alarm

—

Alarm Counter Byte 1

—

06h

Alarm

MSB

Alarm Counter Byte 2

—

07h Control

EOSC ACE 0

0 INTCN RS2 RS1 AIE

08h

Status OSF

0 0 0 0 0 0 AF

09h ID

Model

Number

0Ah

ID

Serial Number Byte 0

0Bh

ID

Serial Number Byte 1

0Ch

ID

Serial Number Byte 2

0Dh

ID

Serial Number Byte 3

0Eh

ID

Serial Number Byte 4

0Fh

ID

Serial Number Byte 5

10h ID

CRC

Table 1. DS1372 Address Map

Note: Unless otherwise specified, the states of the registers are undefined when power is first applied. Bits shown as 0 always read

back as 0.

I

2

C, 32-Bit, Binary Counter Clock with 64-Bit ID