Ds1372, C, 32-bit, binary counter clock with 64-bit id, Electrical characteristics – Rainbow Electronics DS1372 User Manual

Page 2

DS1372

2

_______________________________________________________________________________________

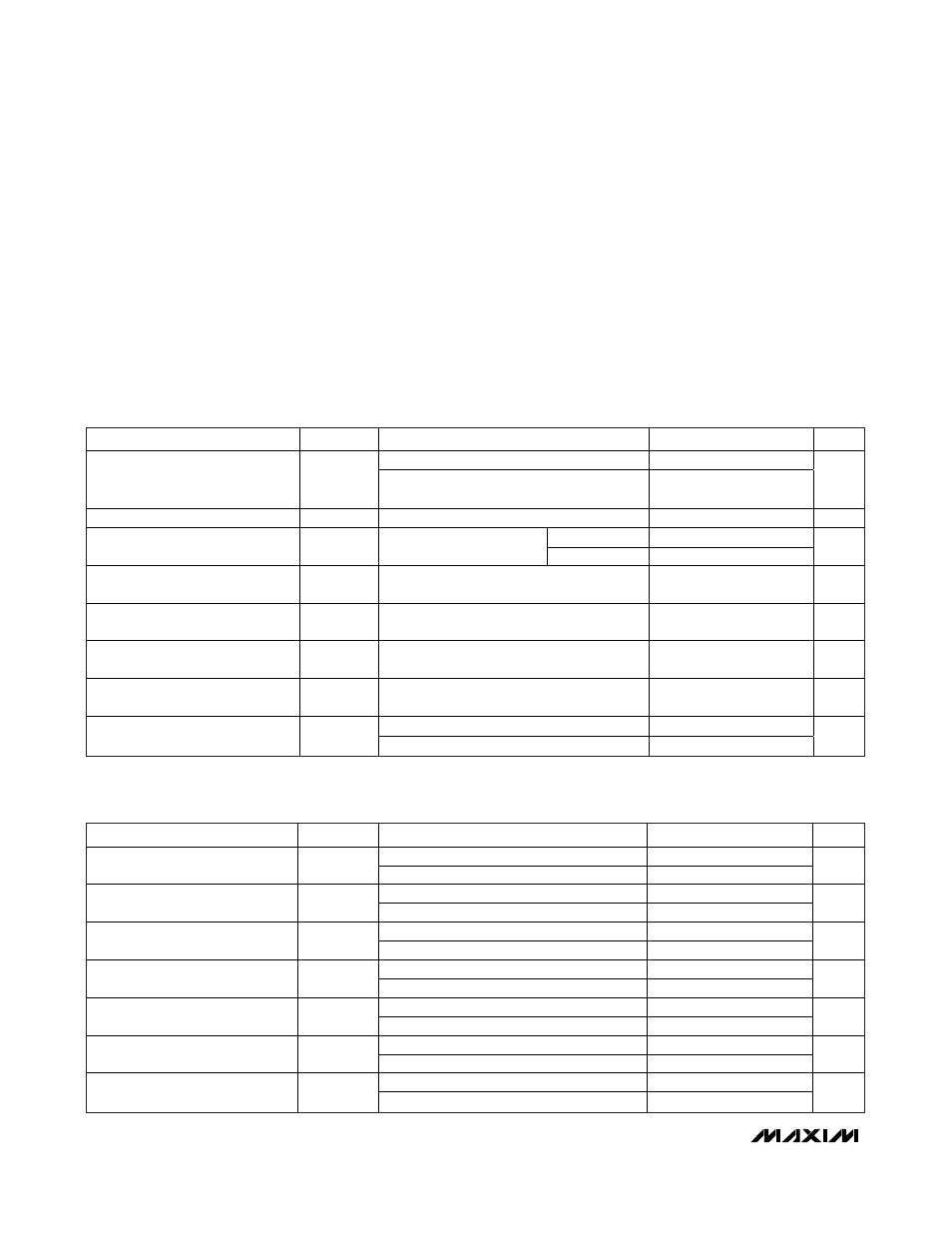

ABSOLUTE MAXIMUM RATINGS

RECOMMENDED DC ELECTRICAL CHARACTERISTICS

(V

CC

= 2.4V to 5.5V, T

A

= -40°C to +85°C, unless otherwise noted.) (Note 1)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Voltage Range on Any Pin Relative to Ground…. .-0.3V to +6.0V

Continuous Power Dissipation (T

A

= +70°C)

(derate 4.5mW/°C above +70°C) ……………………. ....360mW

Operating Temperature Range

(noncondensing)……. .......................................-40°C to +85°C

Storage Temperature Range…………………….-55°C to +125°C

Soldering Temperature………….......See IPC/JEDEC J-STD-020

specification.

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Operating voltage range (Notes 2 and 3)

2.4

5.5

Supply Voltage

V

CC

Timekeeping operating range

(Notes 2 and 4)

1.3 5.5

V

Active Supply Current

I

CCA

(Note 3)

35

90

μA

SQW = 32kHz

600

1300

Standby Current

(Oscillator Enabled)

I

CCS

EOSC = 0

(Notes 4 and 5)

SQW = 0

400

800

nA

Data Retention

(Oscillator Disabled)

I

DDR

EOSC = 1 (Note 4)

25

100

nA

Input Logic 1

AD0, SCL, SDA

V

IH

(Note 2)

0.7 x

V

CC

V

CC

+

0.3

V

Input Logic 0

AD0, SCL, SDA

V

IL

(Note 2)

-0.3

0.3 x

V

CC

V

Input Leakage

AD0, SCL, SDA, SQW/

INT

I

LI

SDA, SQW/

INT high impedance

-1

+1

μA

V

OL

= 0.4V (V

CC

> 2.4V), SDA, SQW/

INT 3

Output Logic 0

I

OL

V

OL

= 0.2V

CC

(1.3V < V

CC

< 2.4V), SQW/

INT

0.250

mA

ELECTRICAL CHARACTERISTICS

(V

CC

= 2.4V to 5.5V, T

A

= -40°C to +85°C, unless otherwise noted.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Fast

mode

100 400

SCL Clock Frequency (Note 6)

f

SCL

Standard mode

0.04

100.00

kHz

Fast mode

1.3

Bus-Free Time Between a STOP

and START Condition

t

BUF

Standard mode

4.7

μs

Fast mode

0.6

Hold Time (Repeated) START

Condition (Note 7)

t

HD:STA

Standard mode

4.0

μs

Fast mode

1.3

Low Period of SCL Clock

t

LOW

Standard mode

4.7

μs

Fast mode

0.6

High Period of SCL Clock

t

HIGH

Standard mode

4.0

μs

Fast mode

0.6

Setup Time for Repeated START

Condition

t

SU:STA

Standard mode

4.7

μs

Fast mode

0

0.9

Data Hold Time (Notes 8 and 9)

t

HD:DAT

Standard mode

0

μs

I

2

C, 32-Bit, Binary Counter Clock with 64-Bit ID