Operation, Wire bus system, Hardware configuration – Rainbow Electronics DS2411 User Manual

Page 4

DS2411

4 of 11

Note 11:

e represents the time required for the pullup circuitry to pull the voltage on I/O up V

IL

to

V

TH

.

Note 12:

d represents the time required for the pullup circuitry to pull the voltage on I/O up from

V

IL

to the input-high threshold of the bus master.

Note 13:

Interval begins when the voltage drops below V

TL

during a negative edge on I/O and ends

when the voltage rises above V

TH

during a positive edge on I/O.

OPERATION

The DS2411’s registration number is accessed through a single data line. The 48-bit serial number, 8-bit

family code, and 8-bit CRC are retrieved using the Dallas 1-Wire protocol. This protocol defines bus

transactions in terms of the bus state during specified time slots that are bus-master-generated falling

edges on the I/O pin. All data is read and written least significant bit first. The device requires a delay

between V

CC

power-up and initial 1-Wire communication, t

PWRP

(1200

ms). During this time the device

may issue presence-detect pulses.

1-Wire BUS SYSTEM

The 1-Wire bus has a single bus master and one or more slaves. In all instances, the DS2411 is a slave

device. The bus master is typically either a microcontroller or a Dallas Semiconductor bridge chip such as

the DS2480, DS2490, or DS1481. The discussion of this bus system is broken down into three topics:

hardware configuration, transaction sequence, and 1-Wire signaling (signal type and timing).

Hardware Configuration

The 1-Wire bus has a single data line, I/O. It is important that each device on the bus be able to drive I/O

at the appropriate time. To facilitate this, each device has an open-drain or three-state output. The

DS2411 has an open-drain output with an internal circuit equivalent to that shown in Figure 3. The bus

master can have the same equivalent circuit. If a bidirectional pin is not available on the master, separate

output and input pins can be connected together. The bus requires a pullup resistor at the master end of

the bus, as shown in Figure 4. A multidrop bus consists of a 1-Wire bus with multiple slaves attached.

The 1-Wire bus has a maximum data rate of 15.4kbps in standard speed and 125kbps in overdrive.

The idle state for the 1-Wire bus is high. If a transaction needs to be suspended for any reason, I/O must

remain high if the transaction is to be resumed. If the bus is pulled low, slave devices on the bus will

interpret the low as either a timeslot, or a reset depending on the duration.

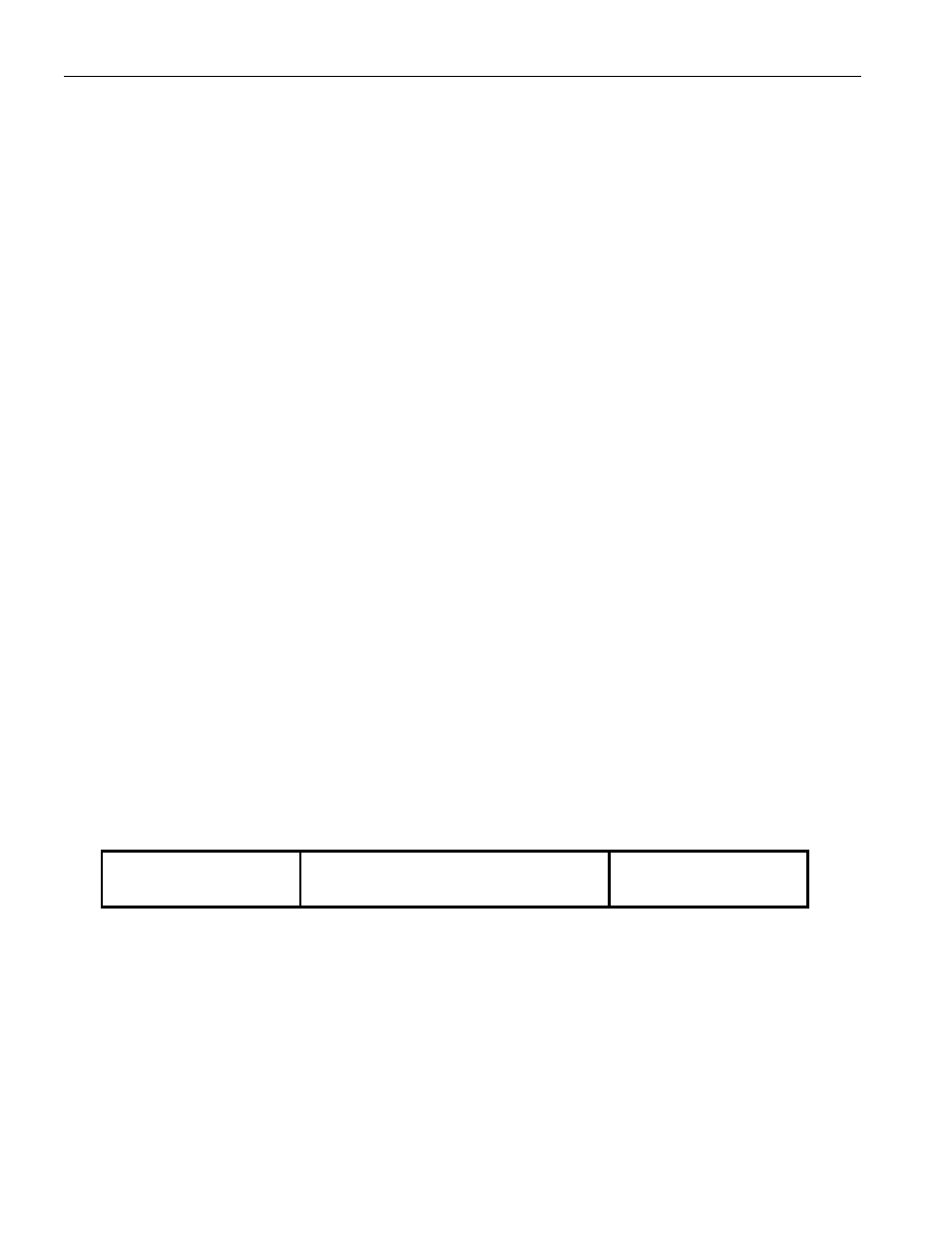

Figure 1. DS2411 REGISTRATION NUMBER

MSB

LSB

8-BIT CRC CODE

48-BIT SERIAL NUMBER

8-BIT FAMILY CODE

(01h)

MSB

LSB MSB

LSB MSB

LSB