Rainbow Electronics DS2411 User Manual

Page 3

DS2411

3 of 11

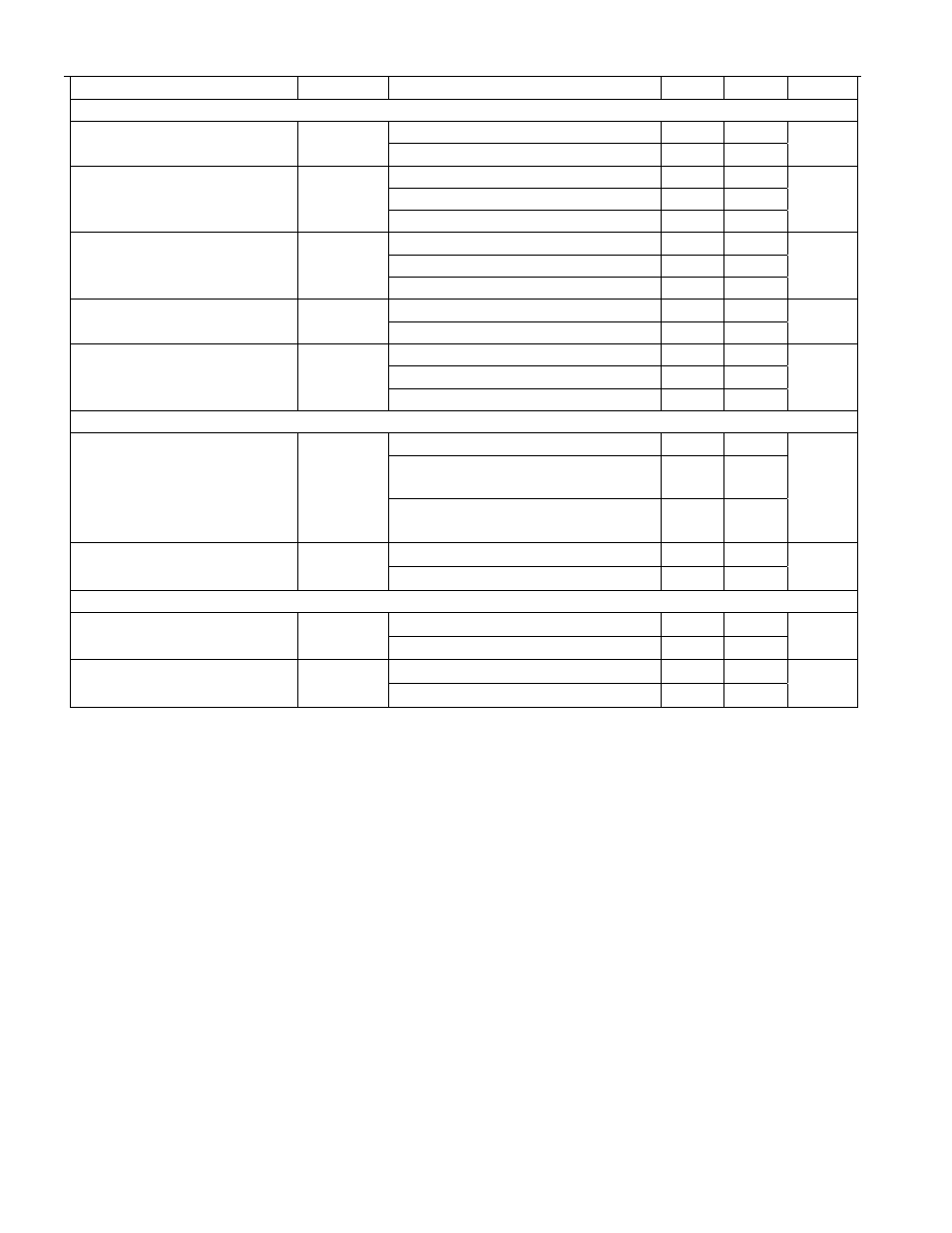

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX UNITS

I/O PIN, 1-Wire RESET, PRESENCE DETECT CYCLE

Standard speed

480

640

Reset Low Time

t

RSTL

Overdrive speed

60

80

µs

Standard speed

15

60

Overdrive V

CC

≥ 2.2V

2

6

Presence-Detect High Time

t

PDH

Overdrive V

CC

≥ 1.5V

2

8.5

µs

Standard speed

60

240

Overdrive V

CC

≥ 2.2V

8

24

Presence-Detect Low Time

t

PDL

Overdrive V

CC

≥ 1.5V

8

30

µs

Standard speed (Note 10, 3)

0.4

8

Presence-Detect Fall Time

t

FPD

Overdrive speed (Note 10, 3)

0.05

1

µs

Standard speed (Note 1)

60

75

Overdrive V

CC

≥ 2.2V (Note 1)

6

10

Presence-Detect Sample

Time

t

MSP

Overdrive V

CC

≥ 1.5V (Note 1)

8.5

10

µs

I/O PIN, 1-Wire WRITE

Standard speed (Notes 1, 13)

60

120

Overdrive V

CC

≥ 2.2V (Notes 1,

13)

6

16

Write-0 Low Time

t

W0L

Overdrive V

CC

≥ 1.5V (Notes 1,

13)

8

16

µs

Standard speed (Notes 1, 11, 13)

5

15 -

e

Write-1 Low Time

t

W1L

Overdrive speed (Notes 1, 11, 13)

1

2 -

e

µs

I/O PIN, 1-Wire READ

Standard speed (Notes 1, 11)

5

15 -

e

Read Low Time

t

RL

Overdrive speed (Notes 1, 11)

1

2 -

e

µs

Standard speed (Notes 1, 12)

t

RL

+

d

15

Read Sample Time

t

MSR

Overdrive speed (Notes 1, 12)

t

RL

+

d

2

µs

Note 1:

System requirement.

Note 2:

Maximum allowable pullup resistance is a function of the number of 1-Wire devices in the

system and 1-Wire recovery times. The specified value here applies to systems with only

one device and with the minimum 1-Wire recovery times. For more heavily loaded

systems, an active pullup such as that found in the DS2480B may be required. Minimum

allowable pullup resistance is slightly greater than the value necessary to produce the

absolute maximum current (20mA) during 1-Wire low times at V

PUP

= 5.25V assuming

V

OL

= 0V.

Note 3:

Not production tested.

Note 4:

V

TL

and V

TH

are functions of V

CC

and temperature.

Note 5:

Voltage below which during a falling edge on I/O, a logic ‘0’ is detected.

Note 6:

Voltage above which during a rising edge on I/O, a logic ‘1’ is detected.

Note 7:

After V

TH

is crossed during a rising edge on I/O, the voltage on I/O has to drop by V

HY

to

be detected as logic ‘0’.

Note 8:

The I-V characteristic is linear for voltages less than 1V.

Note 9:

The earliest recognition of a negative edge is possible at t

REH

after V

TH

has been reached

on the previous edge.

Note 10:

Interval during the negative edge on I/O at the beginning of a presence-detect pulse

between the time at which the voltage is 90% of V

PUP

and the time at which the voltage is

10% of V

PUP

.