Table 1. operating modes, Data read mode, Data write mode – Rainbow Electronics DS1558Y User Manual

Page 5: Data retention mode

DS1558

5 of 18

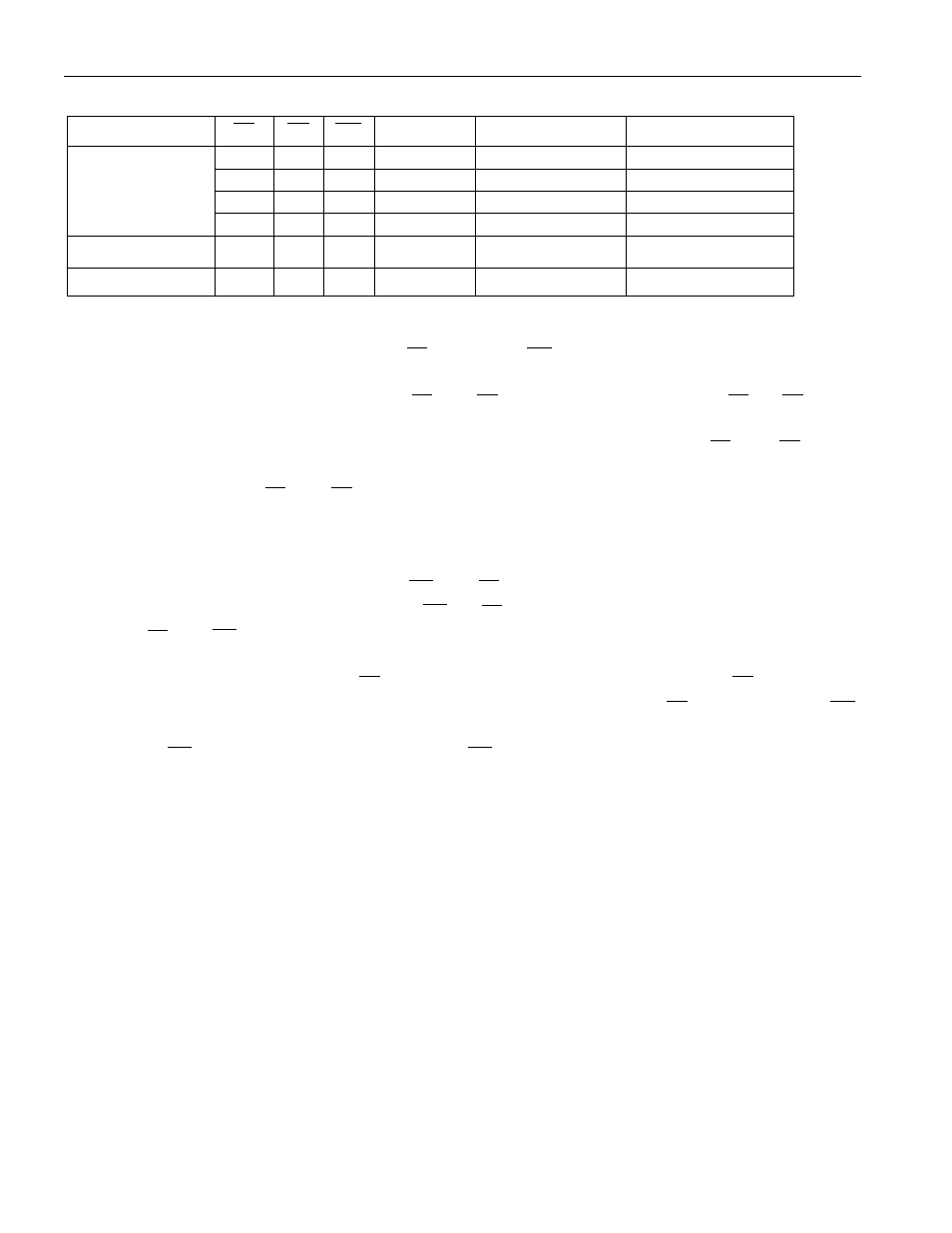

Table 1. OPERATING MODES

V

CC

CE

OE

WE

DQ0–DQ7

MODE

POWER

V

IH

X

X

High-Z

Deselect

Standby

V

IL

X

V

IL

D

IN

Write

Active

V

IL

V

IL

V

IH

D

OUT

Read

Active

V

CC

> V

PF

V

IL

V

IH

V

IH

High-Z

Read

Active

V

SO

< V

CC

< V

PF

X

X

X

High-Z

Deselect

CMOS Standby

V

CC

< V

SO

< V

PF

X

X

X

High-Z

Data Retention

Battery Current

DATA READ MODE

The DS1558 is in the read mode whenever

CE

is low and

WE

is high. The device architecture allows

ripple-through access to any valid address location. Valid data is available at the DQ pins within t

AA

after

the last address input is stable, provided that

CE

and

OE

access times are satisfied. If

CE

or

OE

access

times are not met, valid data is available at the latter of chip-enable access (t

CEA

) or at output-enable

access time (t

OEA

). The state of the data input/output pins (DQ) is controlled by

CE

and

OE

. If the

outputs are activated before t

AA

, the data lines are driven to an intermediate state until t

AA

. If the address

inputs are changed while

CE

and

OE

remain valid, output data remains valid for output-data hold time

(t

OH

), but then goes indeterminate until the next address access.

DATA WRITE MODE

The DS1558 is in the write mode whenever

WE

and

CE

are in their active state. The start of a write is

referenced to the latter occurring transition of

WE

or

CE

. The addresses must be held valid throughout

the cycle.

CE

and

WE

must return inactive for a minimum of t

WR

prior to the initiation of a subsequent

read or write cycle. Data in must be valid t

DS

prior to the end of the write and remain valid for t

DH

afterward. In a typical application, the

OE

signal is high during a write cycle. However,

OE

can be active

provided that care is taken with the data bus to avoid bus contention. If

OE

is low prior to

WE

transitioning low, the data bus can become active with read data defined by the address inputs. A low

transition on

WE

then disables the outputs t

WEZ

after

WE

goes active.

DATA RETENTION MODE

The 5V device is fully accessible and data can be written and read only when V

CC

is greater than V

PF

.

However, when V

CC

is below the power-fail point V

PF

(point at which write protection occurs), the

internal clock registers and SRAM are blocked from any access. When V

CC

falls below the battery switch

point V

SO

(battery supply level), device power is switched from the V

CC

pin to the backup battery. RTC

operation and SRAM data are maintained from the battery until V

CC

is returned to nominal levels.

The 3.3V device is fully accessible and data can be written and read only when V

CC

is greater than V

PF

.

When V

CC

falls below V

PF

, access to the device is inhibited. If V

PF

is less than V

SO

, the device power is

switched from V

CC

to the internal backup lithium battery when V

CC

drops below V

PF

. If V

PF

is greater

than V

SO

, the device power is switched from V

CC

to the internal backup lithium battery when V

CC

drops

below V

SO

. RTC operation and SRAM data are maintained from the battery until V

CC

is returned to

nominal levels.

All control, data, and address signals must be powered down when V

CC

is powered down.